# Using DDR and DDR2 SDRAM in Stratix III and Stratix IV Devices

## August 2008 v2.0

**Application Note 435**

## Introduction

DDR2 SDRAM is the second generation of DDR SDRAM technology, with improvements that include lower power consumption, higher data bandwidth, enhanced signal quality, and on-die termination (ODT) schemes. DDR2 SDRAM brings higher memory performance to a broad range of applications, such as PCs, embedded processor systems, image processing, storage, communications, and networking.

Altera<sup>®</sup> Stratix<sup>®</sup> III and Stratix IV devices support DDR and DDR2 SDRAM interfaces with dedicated DQS circuitry. Table 1 displays the maximum clock frequency for DDR and DDR2 SDRAM in Stratix III devices.

| Stratix III Devices (Part 1 of 2) Notes (1), (2), (3) |      |             |                        |

|-------------------------------------------------------|------|-------------|------------------------|

| Туре                                                  | Rate | Speed Grade | f <sub>MAX</sub> (MHz) |

| DDR SDRAM                                             | Half | -2          | 200                    |

|                                                       |      | -3          | 200                    |

|                                                       |      | -4          | 200                    |

|                                                       |      | -4L (4)     | 200                    |

|                                                       | Full | -2          | 200                    |

|                                                       |      | -3          | 200                    |

|                                                       |      | -4          | 200                    |

|                                                       |      | -4L (4)     | 167                    |

|                                                       |      |             |                        |

Table 1. DDR and DDR2 SDRAM Maximum Clock Frequency Supported in

Stratix III Devices (Part 1 of 2) Notes (1), (2), (3)

| Stratix III Devices (Part 2 of 2) Notes (1), (2), (3) |      |             |                        |

|-------------------------------------------------------|------|-------------|------------------------|

| Туре                                                  | Rate | Speed Grade | f <sub>MAX</sub> (MHz) |

| DDR2 SDRAM                                            | Half | -2          | 400                    |

|                                                       |      | -3          | 333                    |

|                                                       |      | -4          | 333 (5)                |

|                                                       |      | -4L (4)     | 200                    |

| -                                                     | Full | -2          | 267                    |

|                                                       |      | -3          | 233                    |

|                                                       |      | -4          | 200                    |

|                                                       |      | -4L (4)     | 167                    |

|                                                       |      | -4L (4)     | 167                    |

## Table 1. DDR and DDR2 SDRAM Maximum Clock Frequency Supported in Stratix III Devices (Part 2 of 2) Notes (1), (2), (3)

Notes to Table 1:

- (1) Numbers are preliminary until characterization is final. The supported operating frequencies are memory interface maximums for the device family. Your design's actual achievable performance is based on design and system specific factors and static timing analysis of the completed design.

- (2) Applies to both DIMMs and components.

- (3) Applies to both commercial and industrial devices.

- (4) Performance is based on 0.9-V core voltage. At 1.1-V core voltage, the -4L speed grade devices have the same performance as the -4 speed grade devices.

- (5) Timing cannot be closed at the target speed in the Quartus II software version 8.0 but you can generate programming files. You can use these designs for prototyping and testing, but you should not go to production until Altera releases IP that can achieve these speeds.

Table 2 displays the maximum clock frequency for DDR and DDR2 SDRAM in Stratix IV devices.

| Table 2. DDR and DDR2 SDRAM Maximum Clock Frequency Supported in         Stratix IV Devices (Part 1 of 2) Notes (1), (2), (3) |             |                        |  |

|-------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------|--|

| Туре                                                                                                                          | Speed Grade | f <sub>MAX</sub> (MHz) |  |

| DDR SDRAM                                                                                                                     | -2          | 200                    |  |

|                                                                                                                               | -3          | 200                    |  |

|                                                                                                                               | -4          | 200                    |  |

|            | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Speed Grade                                                                             | f <sub>MAX</sub> (MHz)                                                                             |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|            | DDR2 SDRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -2                                                                                      | 400 (4)                                                                                            |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -3                                                                                      | 333                                                                                                |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -4                                                                                      | 333                                                                                                |

|            | <ul> <li>Notes to Table 2:</li> <li>(1) Numbers are preliminary until characterization is final. The supported operating frequencies are memory interface maximums for the device family. Your design's actual achievable performance is based on design, and system specific factors and static timing analysis of the completed design.</li> <li>(2) Applies to both DIMMs and components.</li> <li>(3) Left and right I/O banks do not support 1.5-V HSTL or SSTL Class II I/O standards</li> <li>(4) 400 MHz f<sub>MAX</sub> for Stratix IV E devices in any package and Stratix IV GX devices with 1,152 (24 transceivers), 1,517, and 1,932-pin packages in top and bottom banks only. For left and right banks and for Stratix IV devices with 780 and 1,152-pin packages (16 transceivers), f<sub>MAX</sub> is 300 MHz.</li> </ul> |                                                                                         |                                                                                                    |

|            | This application note describes the FPGA design flow to implement external memory interfaces using Stratix III and Stratix IV devices, and provides design guidelines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |                                                                                                    |

|            | DDR and DDR2 SDRAMs a<br>such as DIMMs, SODIMMs,<br>describes implementing DD<br>IV, or HardCopy III devices,<br>timing analysis, and the gen<br>you may use to demonstrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | and RDIMMs. This a<br>R and DDR2 SDRAM<br>including informatic<br>eration of a complete | application note<br>I with Stratix III, Stratix<br>on on electrical and<br>board-level system that |

|            | Stratix III and Stratix IV dev<br>(IOE) structure, so they effect<br>interface capabilities. HardC<br>have identical capabilities to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ctively have the same<br>Copy III devices may                                           | external memory<br>also be considered to                                                           |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         | made for Stratix III<br>HardCopy III devices,                                                      |

| Background | <ul> <li>This section gives backgroux</li> <li>DDR and DDR2 SDRAI</li> <li>IOE Dedicated DDR an</li> <li>DDR and DDR2 SDRAI</li> <li>ALTMEMPHY Megafur</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | M Overview<br>d DDR2 SDRAM Fea<br>M Interface Terminati                                 | tures                                                                                              |

# Table 2. DDR and DDR2 SDRAM Maximum Clock Frequency Supported in Stratix IV Devices (Part 2 of 2) Notes (1), (2), (3)

## DDR and DDR2 SDRAM Overview

This section gives an overview of DDR SDRAM and DDR2 SDRAM.

## DDR SDRAM Overview

DDR SDRAM is a 2n prefetch architecture with two data transfers per clock cycle. It uses a single-ended strobe, DQS, which is associated with a group of data pins, DQ, for read and write operations. Both DQS and DQ ports are bidirectional. Address ports are shared for read and write operations.

Write and read operations are sent in bursts, DDR SDRAM supports burst lengths of 2, 4, and 8. The column address strobe (CAS) latency is the latency between when the read command is clocked into the memory and the requested data is presented at the memory pins. DDR SDRAM can have CAS latencies of 2, 2.5, and 3, depending on operating frequency.

DDR SDRAM devices use the SSTL-2 2.5V I/O standard and can hold between 64 MB and 1 GB of data. Each device is divided into four banks, and each bank has a fixed number of rows and columns. Only one row per bank can be accessed at a time. The ACTIVE command opens a row and the PRECHARGE command closes a row.

DDR SDRAM has a maximum frequency of 200 MHz or 400 Mbps per DQ pin.

Altera ALTMEMPHY megafunction designs do not support burst lengths of 8.

## DDR2 SDRAM Overview

DDR2 SDRAM is the second generation of the DDR SDRAM standard. It is a 4n prefetch architecture (internally the memory operates at half the interface frequency) with two data transfers per clock cycle. DDR2 SDRAM can use a single-ended or differential strobe, DQS or DQSn, which is associated with a group of data pins, DQ, for read and write operations. DQS, DQSn, and DQ ports are bidirectional. Address ports are shared for read and write operations.

Write and read operations are sent in bursts, DDR2 SDRAM supports burst lengths of 4 and 8. DDR2 SDRAM supports CAS latencies of 2, 3, 4, and 5.

DDR2 SDRAM devices use the SSTL-18 1.8-V I/O standard and can hold between 256 MB and 4 GB of data. All DDR2 SDRAM devices have at least four banks, but higher-density devices (typically 1 GB and above)

have eight internal banks. With more banks available, the page-to-hit ratio is twice as great when compared to DDR SDRAM. DDR2 SDRAM also allows bank interleaving, which represents a significant advantage for applications accessing random data. Bank interleaving can be extremely effective for concurrent operations and can hide the timing overhead that are otherwise required for opening and closing individual banks.

DDR2 SDRAM also supports ODT signal options of 50, 75, or 150  $\Omega$  on all DQ, DM, and DQS and DQSn signals.

DDR2 SDRAM has a maximum frequency of 533 MHz or 1,066 Mbps per DQ pin.

## DDR and DDR2 SDRAM Comparison

Table 3 compares DDR and DDR2 SDRAM features.

| Table 3. DDR and DDR2 SDRAM Features (Part 1 of 2) |                           |                             |                                                                                                |

|----------------------------------------------------|---------------------------|-----------------------------|------------------------------------------------------------------------------------------------|

| Feature                                            | DDR SDRAM                 | DDR2 SDRAM                  | DDR2 SDRAM Advantage                                                                           |

| Voltage                                            | 2.5 V                     | 1.8 V                       | Reduces memory system power demand.                                                            |

| Density                                            | 64 MB to 1GB              | 256 MB to 4 GB              | High-density components simplify memory subsystem.                                             |

| Internal banks                                     | 4                         | 4 and 8                     | Page-to-hit ratio increased.                                                                   |

| Prefetch                                           | 2                         | 4                           | Lower memory core speed results<br>in higher operating frequency and<br>lower power operation. |

| Speed                                              | 100 MHz to 200 MHz        | 200 MHz to 533 MHz          | Higher data rate.                                                                              |

| Read latency                                       | 2, 2.5, 3 clocks          | 3, 4, 5 clocks              | Eliminating half clock setting allows 4n prefetch architecture.                                |

| Additive latency (1)                               | —                         | 0, 1, 2, 3, 4               | Improves command efficiency.                                                                   |

| Write latency                                      | One clock                 | Read latency – 1            | Improves command efficiency.                                                                   |

| Termination                                        | PCB, discrete to $V_{TT}$ | Discrete to $V_{TT}$ or ODT | Improves signaling, eases PCB layout, reduces system cost.                                     |

Altera ALTMEMPHY megafunction-based designs do not support burst lengths of 8.

Altera DDR and DDR2 SDRAM High-Performance Controllers do not support bank interleaving.

| Table 3. DDR and DDR2 SDRAM Features (Part 2 of 2) |              |                                  |                         |

|----------------------------------------------------|--------------|----------------------------------|-------------------------|

| Feature                                            | DDR SDRAM    | DDR2 SDRAM                       | DDR2 SDRAM Advantage    |

| Data strobes                                       | Single-ended | Differential or single-<br>ended | Improves timing margin. |

Note to Table 3:

(1) The Altera SDRAM high-performance controllers do not support additive latency.

## **IOE Dedicated DDR and DDR2 SDRAM Features**

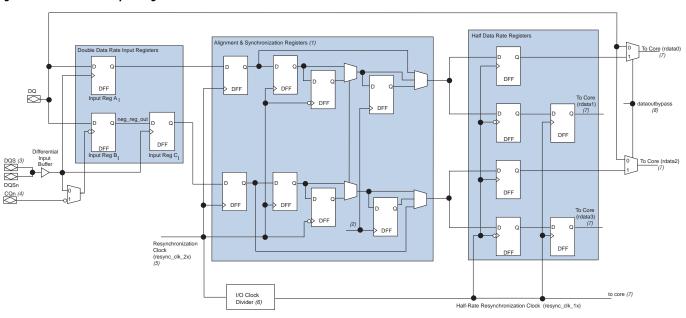

Stratix III devices have enhanced upon the IOE DDR capabilities of previous generations of devices by including the following functionality availability directly in the IOE.

- DDR registers

- Alignment and synchronization registers (including I/O clock divider)

- Half data-rate registers

- DQS phase-shift circuitry (up to 4 two-phase-offset DLLs)

- DQS postamble circuitry

- Single-ended, differential or complementary DQS mode

- Read and write leveling circuitry

- Dynamic on-chip termination (OCT) control

To use these features you should use the Altera DDR and DDR2 SDRAM High-Performance Controller (a complete solution) or the Altera ALTMEMPHY megafunction (for a fully configured PHY that requires an additional custom or third-party memory controller).

Alternatively, you may access these IOE features directly via the following low-level megafunctions:

- ALTDQ\_DQS megafunction—allows you to parameterize the following features:

- DDR

- alignment and synchronization

- half data rate

- DQS mode

- ALTDLL megafunction—allows you to parameterize the DQS phase-shift circuitry

- ALTOCT megafunction—allows you to parameterize the IOE OCT features.

- ALTPLL megafunction—allows you to parameterize the device PLL

- ALTIOBUF megafunction—allows you to parameterize the device IO

## Device Pin Utilization

Table 4 shows the DDR and DDR2 SDRAM interface pins and how to connect them to Stratix III pins.

| Table 4. Stratix III DDR and DDR2 SDRAM Interface Pin Utilization |                    |                                                                                                                                                                                                                       |  |

|-------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin                                                               | Pin Planner Symbol | Stratix III Pin                                                                                                                                                                                                       |  |

| DQ                                                                | Q                  | DQ. Each DQ group has a common background                                                                                                                                                                             |  |

| DM                                                                | Q                  | color for all of the associated DQ and DM pins.                                                                                                                                                                       |  |

| Differential DQS or DQSn (DDR2 only)                              | S or Sbar          | DQS or DQSn. DDR2 supports either single-ended or differential DQS signaling.                                                                                                                                         |  |

| Single-ended DQS                                                  | S                  | DQS.                                                                                                                                                                                                                  |  |

| <pre>mem_clk[0] or mem_clk_n[0]</pre>                             | _                  | Any unused DIFFIO_RX pins in the same bank or side for DDR2 SDRAM interfaces with differential DQS signaling. (1)                                                                                                     |  |

|                                                                   | _                  | Any DIFFOUT pins for DDR2 SDRAM (with single-<br>ended DQS signaling) and DDR SDRAM.                                                                                                                                  |  |

| <pre>mem_clk[n:1]or mem_clk_n[n:1]</pre>                          | _                  | Any DIFFOUT pins for DDR2 and DDR SDRAM (where n is greater than or equal to 1)                                                                                                                                       |  |

| Address and command                                               | _                  | <ul> <li>Any user I/O pin. To minimize skew, you should place address and command pins in the same bank or side of the device as the following pins:</li> <li>mem_clk* pins.</li> <li>DQ, DQS, or DM pins.</li> </ul> |  |

| Clock source                                                      | _                  | Dedicated PLL clock input pin with direct (not using<br>a global clock net) connection to the PLL and<br>optional DLL required by the interface.                                                                      |  |

| Reset                                                             | —                  | Dedicated clock input pin (high fan-out signal).                                                                                                                                                                      |  |

#### Note to Table 4:

(1) ALTMEMPHY mimic path requirement only.

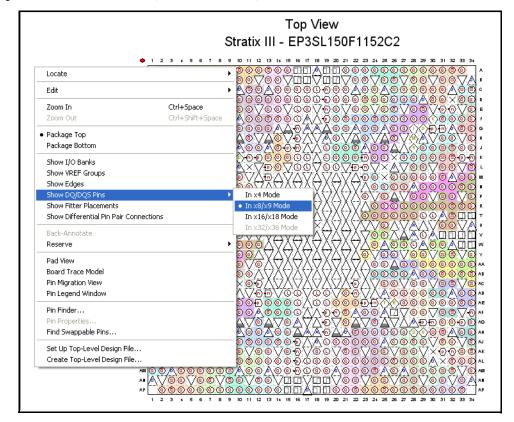

## DQ and DQS Group Interface Width

For maximum performance and best skew across the interface, you should select a device where each required memory interface can completely reside within a single bank, or at least one side of the device.

Maximum interface width varies from device to device depending on the number of I/Os and DQS and DQ groups available. The smallest 480-pin device sizes can typically support a 128-MB 16-bit wide complete interface in both the top and bottom banks and a 32-bit wide complete interface in side banks. The largest 1,760-pin devices can support a 72-bit wide DQ interface in each left and right banks. Achievable interface

width depends on the number of address and command pins that the design requires. To ensure adequate PLL, clock and device routing resources are available, you should always test fit any IP in the Quartus II software before PCB sign-off.

Table 5 shows the number of DDR and DDR2 SDRAM suitable DQS and DQ groups available in Stratix III devices per side.

| Package       | Side           | x4 | x8/x9 |

|---------------|----------------|----|-------|

| 484-pin BGA   | Top and bottom | 5  | 2     |

|               | Left and right | 12 | 4     |

| 780-pin BGA   | Top and bottom | 17 | 8     |

|               | Left and right | 14 | 6     |

| 1,152-pin BGA | Top and bottom | 26 | 12    |

|               | Left and right | 26 | 12    |

| 1,517-pin BGA | Top and bottom | 38 | 18    |

|               | Left and right | 34 | 16    |

| 1,760-pin BGA | Top and bottom | 44 | 22    |

|               | Left and right | 40 | 18    |

#### Note to Table 5:

- (1) Numbers are preliminary.

- (2) Some DQS or DQ pins are dual purpose and can also be required as RUP, RDN, or configuration pins. A DQS or DQ group is lost if you use these pins for configuration or as RUP or RDN pins for calibrated OCT. Ensure that the DQS and DQ groups are not also required for configuration or calibrated OCT.

•••

For more information, refer to the *External Memory Interfaces* chapter of the *Stratix III Device Handbook* and the *External Memory Interfaces* chapter of the *Stratix IV Device Handbook*.

#### DDR and DDR2 SDRAM Interface Pin Description

This section describes the DDR and DDR2 SDRAM interface pin description.

#### **Clock Signals**

DDR2 SDRAM devices use CK and CK# signals to clock the address and command signals into the memory. Furthermore, the memory uses these clock signals to generate the DQS signal during a read through the DLL inside the memory. The DDR2 SDRAM data sheet specifies the following timings:

- t<sub>DQSCK</sub> is the skew between the CK or CK# signals and the DDR3 SDRAM-generated DQS signal

- t<sub>DSH</sub> is the DQS falling edge from CK rising edge hold time

- t<sub>DSS</sub> is the DQS falling edge from CK rising edge setup time

- t<sub>DQSS</sub> is the positive DQS latching edge to CK rising edge

- t<sub>DQSCK</sub> is the DQS output access time from CK

The DDR2 SDRAM has a write requirement ( $t_{DQSS}$ ) that states the positive edge of the DQS signal on writes must be within  $\pm$  25% ( $\pm$  90°) of the positive edge of the DDR2 SDRAM clock input. Therefore, you should generate the CK and CK# signals using the DDR registers in the IOE to match with the DQS signal and reduce any variations across process, voltage, and temperature. The positive edge of the DDR2 SDRAM clock, CK, is aligned with the DQS write to satisfy  $t_{DOSS}$ .

The Altera SDRAM high-performance controllers can generate the CK and CK# signals using the DDR registers in the IOE to match with the DQS signal and reduce any variations across process, voltage, and temperature.

#### Strobes, Data, DM, and Optional ECC Signals

The DQS is bidirectional. The DQSn pins in DDR2 SDRAM devices are optional but recommended for DDR2 SDRAM designs operating at more than 333 MHz. Differential DQS operation enables improved system timing due to reduced crosstalk and less simultaneous switching noise on the strobe output drivers. The DQ pins are also bidirectional. Regardless of interface width, DDR SDRAM always operates in ×8 mode DQS groups. DDR2 SDRAM interfaces can operate in either ×4 or ×8 mode DQS groups, which is dependant on your chosen memory device or DIMM, and is also not related to the actual interface width. The ×4 and ×8 configurations use one pair of bidirectional data strobe signals, DQS and DQSn, to capture input data. However, two pairs of data strobes, UDQS and UDQS# (upper byte) and LDQS and LDQS# (lower byte), are required by the ×16 configuration devices. A group of DQ pins must remain associated with its respective DQS and DQSn pins.

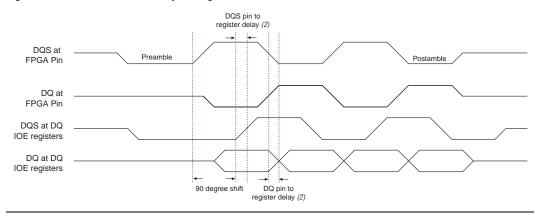

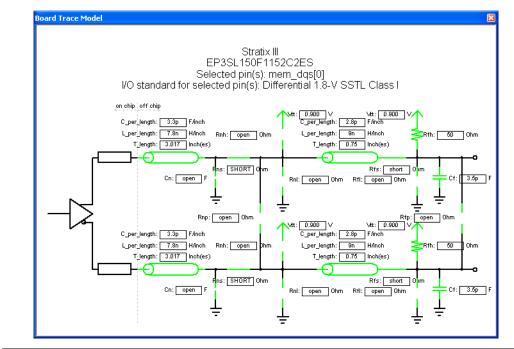

The DQ signals are edge-aligned with the DQS signal during a read from the memory and are center-aligned with the DQS signal during a write to the memory. The memory controller shifts the DQ signals by –90° during a write operation to center align the DQ and DQS signals. The memory controller delays the DQS signal during a read, so that the DQ and DQS signals are center aligned at the capture register. Stratix III devices use a phase-locked loop (PLL) to center-align the DQS signal with respect to the DQ signals during writes and use dedicated DQS phase-shift circuitry to shift the incoming DQS signal during reads. Figure 1 shows an example where the DQS signal is shifted by 90° for a read from the DDR2 SDRAM.

Figure 1. DQ and DQS Relationship During a DDR2 SDRAM Read in Burst-of-Four Mode

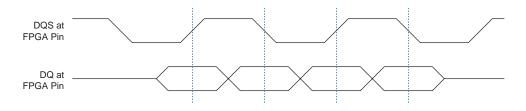

Figure 2 shows an example of the relationship between the data and data strobe during a burst-of-four write.

The memory device's setup ( $t_{DS}$ ) and hold times ( $t_{DH}$ ) for the write DQ and DM pins are relative to the edges of DQS write signals and not the CK or CK# clock. Setup and hold requirements are not necessarily balanced in in DDR2 SDRAM, unlike in DDR SDRAM devices.

The DQS signal is generated on the positive edge of the system clock to meet the  $t_{DQSS}$  requirement. DQ and DM signals use a clock shifted  $-90^{\circ}$  from the system clock, so that the DQS edges are centered on the DQ or DM signals when they arrive at the DDR2 SDRAM. The DQS, DQ, and DM board trace lengths need to be tightly matched (20 ps).

DDR2 SDRAM uses the DM pins during a write operation. Driving the DM pins low shows that the write is valid. The memory masks the DQ signals if the DM pins are driven high. While you can use any of the I/O pins in

the same bank as the associated DQS and DQ pins, to generate the DM signal, Altera recommends that you use the spare DQ pin within the same DQS group as the respective data, to minimize skew.

The DM signal's timing requirements at the DDR2 SDRAM input are identical to those for DQ data. The Stratix III DDR registers, clocked by the  $-90^{\circ}$  shifted clock, create the DM signals.

Some DDR2 SDRAM devices support error correction coding (ECC) to detect and automatically correct error in data transmission. The 72-bit DDR2 SDRAM modules contain eight ECC pins in addition to 64 data pins. Connect the eight DDR2 SDRAM device ECC pins to a single DQS or DQ group.

#### Address and Command Signals

Address and command signals in DDR2 SDRAM devices are clocked into the memory device using the CK or CK# signal. These pins operate at single data rate (SDR) using only one clock edge. The number of address pins depends on the DDR2 SDRAM device capacity. The address pins are multiplexed, so two clock cycles are required to send the row, column, and bank address. The CS, RAS, CAS, WE, CKE, and ODT pins are DDR2 SDRAM command and control pins.

The DDR2 SDRAM address and command inputs do not have a symmetrical setup and hold time requirement with respect to the DDR2 SDRAM clocks, CK, and CK#.

For SDRAM high-performance controllers in Stratix III devices, the address and command clock is always one of the PLL dedicated clock outputs whose phase can be adjusted to meet the setup and hold requirements of the memory clock. The address and command clock is also typically half-rate, although a full-rate implementation can also be created. The command and address pins use the DDIO output circuitry to launch commands from either the rising or falling edges of the clock. The chip select (CS\_N) clock enable (CKE) and ODT pins are only enabled for one memory clock cycle and can be launched from either the rising or falling edge of the address and other command pins are enabled for two memory clock cycles and can also be launched from either the rising or falling edge of the address and command clock signal.

P

In ALTMEMPHY-based solutions, the address and command clock ac\_clk\_1x is always half rate. However, because of the output enable assertion, CS\_N, CKE, and ODT behave like fullrate signals even in a half-rate PHY.

## PLL and DLL Features and Availability

Stratix III devices use PLLs to generate the memory controller clocks. The simplest slowest speed memory controllers may only require two clocks (0° system clock and –90° write clock). However, as interface speeds increase, it becomes harder to close timing and so dedicated resynchronization, postamble, and address and command clocks are typically required. Additionally, at higher frequencies maximum frequency becomes the bottleneck and half-rate designs are the typical solution. Thus complex half high data rate designs require typically 10 clock networks (refer to the *External DDR Memory PHY Interface (ALTMEMPHY) Megafunction User Guide*).

Stratix III devices are well equipped to address the clocking requirements of external DDR and DDR2 SDRAM interfaces. Stratix III PLLs have an increased number of outputs and global clock routing resources when compared to earlier device generations. Stratix III top and bottom PLLs feature 10 output (C) counters, also left and right PLLs feature 7 output (C) counters. This increased number of PLL outputs allows for the use of dedicated clock phases. In previous Stratix II designs, clock phases had to be shared.

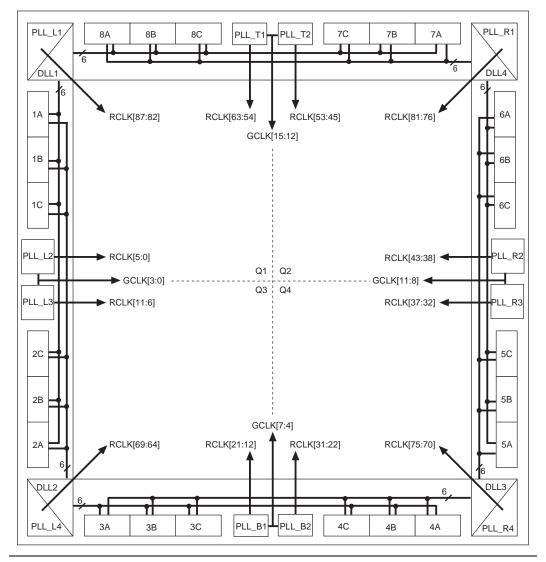

In general, each Stratix III PLL has access to 4 global clocks (GCLK) and 6 regional clocks (RCLK) (left and right) or 10 RCLK (top and bottom).

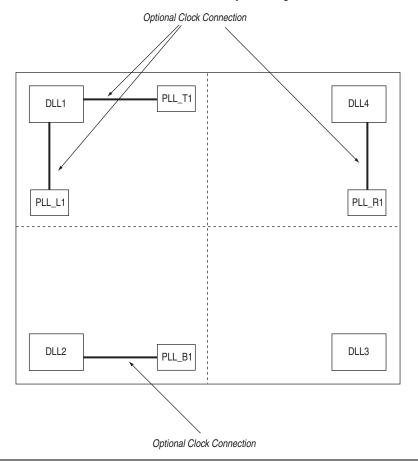

Stratix III devices also feature four DLLs (one located in each corner of the device). The FPGA can support a maximum of four unique frequencies, with each DLL running at one frequency. Each DLL can also support two different phase offsets, which allow a single Stratix III device to support eight different DLL phase shift settings. Additionally, each DLL can access the two sides adjacent to its location. Thus each I/O bank is accessible by two different DLLs, giving more flexibility when creating multiple frequency and phase shift memory interfaces. Figure 3 shows PLL and DLL locations in Stratix III devices with global and regional clock resources.

For more information, refer to the *Clock Networks and PLLs in Stratix III Devices* chapter and the *External Memory Interfaces* chapter in the *Stratix III Device Handbook*.

Figure 3. PLL and DLL Locations and Resources in Stratix III Devices

## IOE Registers

Stratix III IOE registers include the following feature enhancements, over the previous generation of devices, which greatly simplify high speed memory interface design:

- Single-ended or differential DQS signaling

- Alignment and synchronization registers

- Half data rate registers

- I/O clock divider

- Programmable delay

- Read and write leveling—one per subbank. For example, bank 1a, 1b, and 1c = three circuits

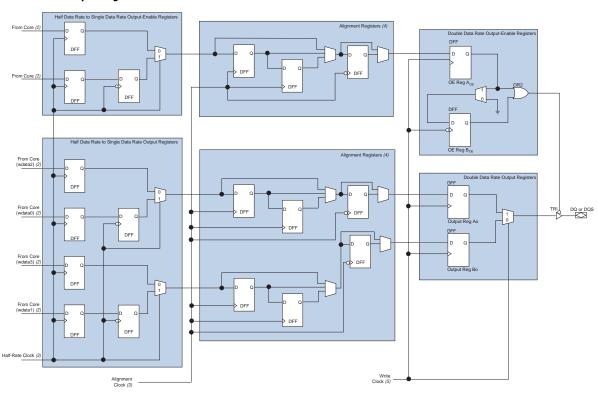

Figure 4 and Figure 5 show the Stratix III IOE structure.

#### Figure 4. Stratix III IOE Input Registers

Background

#### Notes:

- (1) You can bypass each register except the first in this path.

- (2) The 0-phase resynchronization clock from the read-leveling delay chain.

- (3) The input clock can be from the DQS logic block (whether the postamble circuitry is bypassed or not) or from a global clock line.

- (4) This input clock comes from the CQn logic block.

- (5) This resynchronization clock can come either from the PLL or from the read-leveling delay chain.

- (6) The I/O clock divider resides adjacent to the DQS logic block. In addition to the PLL and read-levelled resynchronization clock, the I/O clock divider can also be fed by the DQS bus or CQn bus.

- (7) The half-rate data and clock signals feed into a dual-port RAM in the FPGA core.

- (8) You can dynamically change the dataoutbypass signal after configuration.

## Figure 5. Stratix III IOE Output Registers

#### Notes:

- (1) You can bypass each register block of the output and output-enable paths.

- (2) Data coming from the FPGA core are at half the frequency of the memory interface.

- (3) Half-rate and alignment clocks come from the PLL.

- (4) These registers are only used in DDR3 SDRAM interfaces.

- (5) The write clock can come from either the PLL or the write leveling delay chain. There is a 90° offset between the DQ write clock and DQS write clock.

#### Single-ended or Differential DQS Signaling

Stratix III devices directly support differential DQS mode and the singleended standard supported in previous device families. While DDR SDRAM only supports single-ended DQS, DDR2 SDRAM additionally includes the option of differential DQS signaling.

Differential DQS signaling is recommended for DDR2 SDRAM designs operating at or above 333 MHz. Differential DQS strobe operation enables improved system timing due to reduced crosstalk and less simultaneous switching noise on the strobe output drivers. You can use single-ended DQS mode for DDR2 SDRAM interfaces, but it requires more pessimistic timing data and hence results in less system timing margin.

#### **DDR Registers**

Similar to the previous generation of devices, DDR registers are provided on all sides of the device so that DDR I/O structures can be directly implemented in the IOE, thus saving core logic and ensuring tight skew is easily maintained, which eases timing. Stratix III devices now feature four DLLs, so DQS capture mode is now supported on every side of the device.

#### Alignment and Synchronization Registers

In previous device families the resynchronization registers had to be located in the core of the device, which made the placement of these registers with respect to the DDR IOE critical to ensure that timing is achieved. Stratix III devices have been enhanced to include the alignment and synchronization registers directly within the IOE, hence timing is now significantly improved and you are no longer concerned with ensuring critical register placement with respect to the DDR IOE. Typically, the resynchronization register is clocked via a dedicated output from the PLL. However, it may also be clocked directly from the readleveling delay chain. The output alignment registers are typically clocked from the PLL.

Generally alignment and synchronization registers are optional and can be bypassed if not required; for ALTMEMPHY-based designs, these registers are required.

Regardless of interface speed, ALTMEMPHY always implements synchronization registers. Hence latency through the PHY may not be optimal for lower frequency designs.

Stratix III devices include only one leveling delay chain per I/O subbank. For example, subbank 1A includes a single leveling chain, 1B includes a second leveling chain, and so on.

If the resynchronization clock is sourced from the leveling delay chain, it may be cascaded from bank to bank, say 1A to 1B. In this configuration memory controllers must form a single contiguous block of DQS groups that are not staggered or interleaved with another memory controller.

#### Half Data Rate Registers

As external memory interface clock speeds increase, the core  $f_{MAX}$  can become the limiting factor in interface design. A common solution, which increases core  $f_{MAX}$  timing problems, is to implement a half data rate architecture. This solution has the effect of doubling the data width on the core side interfaces compared to a full-rate SDR solution, but also halves the required operating frequency. To simplify PHY design and provide easier design constraints, Stratix III devices include dedicated full-rate to half-rate registers within the IOE.

#### **Clock Divider**

To simplify and reduce the number of clocks required, a dedicated I/O clock divider is provided on a per DQS group basis, which can directly source the half-rate resynchronization clock from the full rate version.

To ease data alignment, a single I/O clock divider may be used for an entire interface, as the half rate resynchronization clock can be cascaded from DQ group to the adjacent DQ group. Hence, when using a common I/O clock divider, the high and low bit order may be performed across the entire interface. Individual I/O clock dividers require the data alignment to be performed on a DQ group basis.

ALTMEMPHY-based designs use a single I/O clock divider when operating in half-rate mode to reduce PHY complexity and reduce latency. Hence, ALTMEMPHY-based interfaces operating in half-rate mode cannot be interleaved.

## **Programmable Delay**

Stratix III I/O registers include programmable delay chains that you may use to deskew interfaces. Each pin can have different delay settings, hence read and write margins can be increased as uncertainties between signals can be minimized.

ALTMEMPHY-based designs do not use dynamic delay chains to deskew interfaces.

#### **Read and Write Leveling**

Stratix III I/O registers include read and write leveling circuitry to enable skew to be removed or applied to the interface on a DQS group basis. There is one leveling circuit located in each I/O subbank.

ALTMEMPHY-based designs for DDR and DDR2 SDRAM do not use leveling circuitry, as it add latency. DDR and DDR2 SDRAM interfaces typically have balanced well-matched PCB delays and use a synchronized single-cycle clock structure.

## IOE OCT Features

Stratix III devices support dynamic calibrated OCT—previous Stratix devices did not. This feature allows the specified series termination to be enabled during writes, and parallel termination to be enabled during reads. In addition to series OCT, Stratix III devices also allow slew rate control to be applied with drive strength options. These I/O features allow you to greatly simplify PCB termination schemes.

For further information, refer to the *Stratix III Device I/O Features* chapter in the *Stratix III Device Handbook* and *AN 408: DDR2 Memory Interface Termination, Drive Strength, and Loading Design Guidelines.*

## DDR and DDR2 SDRAM Interface Termination and Topology

This section discusses signal topology and termination of DDR and DDR2 SDRAM interfaces.

For more information, refer to memory vendor application notes and *AN* 408: *DDR2 Memory Interface Termination, Drive Strength, and Loading Design Guidelines*.

All DDR and DDR2 SDRAM interfaces use the following two classes of signal type:

- Unidirectional class I terminated signals, which include clocks, and address and command signals

- Bidirectional class II terminated signals, which include DQS, DQ, and DM signals

- Although DM is output only, it typically has the same termination and topology as the DQ and DQS pins, to ensure identical timing characteristics.

In general, the only significant difference between electrical DDR and DDR2 SDRAM interfaces is that DDR SDRAM interfaces use the SSTL (2.5-V) I/O standard, and DDR2 SDRAM interfaces use the SSTL18 (1.8-V) I/O standard. In both cases, the V<sub>TT</sub> power source must be specified to both source and sink current.

## Unidirectional Class I Terminated Signals

All class I signals are multiload signals—they either go to a DIMM that has multiple memory devices, or they go to all memory devices that make up the interface. Altera recommends the ideal topology is a balanced symmetrical tree. Altera recommends that the class I termination to  $V_{TT}$  is placed:

- At the DIMM connector (for interfaces using DIMMs)

- At the first split or division of the symmetrical tree for discrete devices

Nonsymmetrical topologies or DIMMs result in over or undershoot and oscillations on the line, which may require compensation capacitors or a lower than ideal drive strength to be specified resulting in derated interface performance.

Memory clocks are typically chosen to ensure an even and matched number of loads on each clock pair, so that the timing to each memory device is consistent assuming equal trace delays. Each clock pair should be loaded to ensure that significant slew rate distortion does not occur. Memory clocks are typically differentially terminated with an effective 100- $\Omega$  resistance. You can achieve 100- $\Omega$  differential termination in one of the following ways:

- **1**00-Ω single resistor directly between the positive and negative signal.

- $50-\Omega$  single-ended resistor to V<sub>TT</sub> on each positive and negative pin.

- 100-Ω up to V<sub>CC</sub> and 100 Ω down to ground on each positive and negative pin.

Electrically all these solutions look the same to differential AC signals.

For information about the electrical I/O termination, refer to the *Stratix Device I/O Features* chapter of the *Stratix III Device Handbook*.

FPGA drive strength and series termination setting should maximize edge rate while ensuring that over or undershoot are not encountered.

The combined use of drive strength and slew rate, or output series termination options mean Stratix III is ideally configurable for any Class I termination schemes.

For further information, refer to *Micron Technical Note TN4720: Point-to-Point Package Sizes and Layout Basics.*

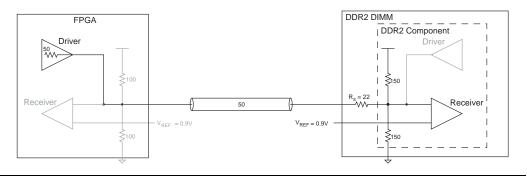

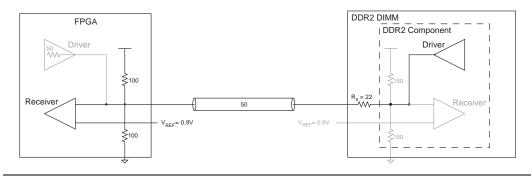

#### Bidirectional Class II Terminated Signals

Class II signals are typically point-to-point, unless you are using either:

- Multiple DIMMs

- Stacked or dual rank DIMMs or topologies

Stratix III devices include on-chip series and parallel termination. So, generally, discrete termination at the FPGA end of the line is not required.

DDR2 SDRAM devices support dynamic parallel ODT at the memory end of the line. So, typically, discrete termination is not required at the memory end of the line.

DDR SDRAM devices do not include ODT. So, generally, parallel termination is required at the memory end of the line.

DDR and DDR2 SDRAM DIMMs include a series terminator and DDR2 SDRAM includes drive strength control. So if you are using DIMMs, a series terminator at the memory end of the line is never required.

For more information, refer to *Micron Technical Note TN-47-01: DDR2 Design Guide for Two-DIMM Systems*.

ALTMEMPHY-based designs do not support multiple DIMMs or dual-rank stacked topologies, because calibration only takes place on the first rank.

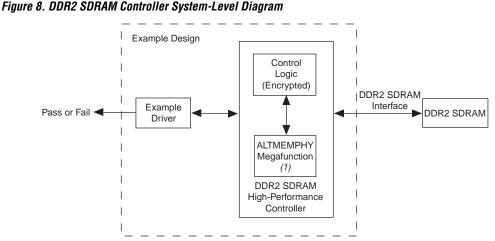

## ALTMEMPHY Megafunction Overview

The Altera ALTMEMPHY megafunction allows the rapid creation of a physical layer interface (PHY) in Stratix III devices. The PHY safely transfers data between memory and user logic. The easy-to-use ALTMEMPHY megafunction GUI enables the rapid configuration of the highly configurable PHY. You can use the ALTMEMPHY megafunction with either a user-designed controller or the Altera DDR and DDR2 SDRAM High-Performance Controllers. You can parameterize the ALTMEMPHY megafunction to support the following features:

- Full-rate or a half-rate operation

- Single-ended or differential DQS mode

- Dynamic termination

The ALTMEMPHY megafunction supports an initial calibration sequence to minimize the effect of process variations in the FPGA and memory device. During operation, the voltage and temperature (VT) tracking mechanism eliminates the effects on timing margin of VT variation. The calibration process centers the resynchronization clock phase into the middle of the data valid window, to maximize the setup and hold margin.

Additionally, the ALTMEMPHY megafunction automatically generates all required TimeQuest timing constraints.

All published Stratix III DDR and DDR2 SDRAM performance data assume the design uses the ALTMEMPHY megafunction.

Altera recommends the use of an ALTMEMPHY-based DDR or DDR2 SDRAM design whenever possible. However, in some situations a simpler ALTDQ\_DQS solution may be preferred and potentially more optimal.

For more information, refer to the *External DDR Memory PHY Interface* (*ALTMEMPHY*) *Megafunction User Guide*.

For more information, refer to the *ALTDLL and ALTDQ\_DQS Megafunctions User Guide*.

# DDR and DDR2 SDRAM in Stratix III Devices Design Flow

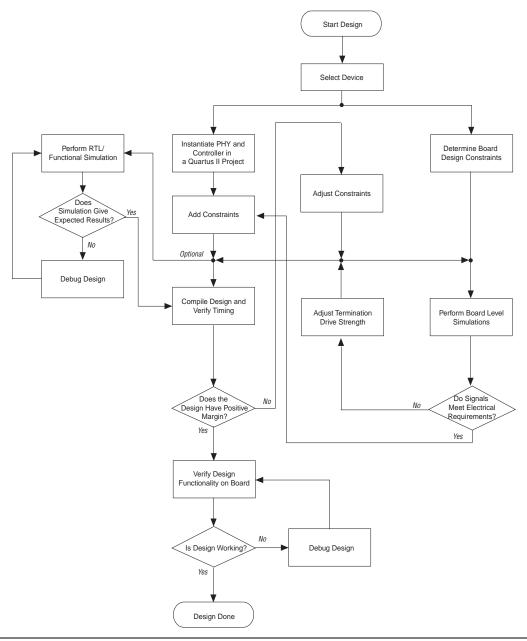

Altera recommends the design guidelines described in this section as best practices for successful memory interface implementation in Stratix III devices. These guidelines provide the fastest out-of-the-box experience with external memory interfaces in Stratix III devices. Figure 6 shows the design flow required for Stratix III memory interfaces. Each step is discussed in detail in the following sections. This flow uses the DDR2 SDRAM High-Performance Controller.

Figure 6. Design Flow for Implementing External Memory Interfaces in Stratix III Devices

## **Select a Device**

This section discusses the following topics:

- Bandwidth

- Full or Half Rate SDRAM Controller

- PLL and Clock Usage

- DLL Usage and Sharing

- Top, Bottom, Left, Right, and Hybrid Device Sides

- DQ and DQS Width Limits

- Address and Command, Clock, and Other Signals

Memory controllers in Stratix III devices require access to dedicated IOE features, PLLs, and several clock networks. Stratix III devices are feature rich in all of these areas, so you must consider detailed resource and pin planning whenever implementing complex IP or multiple IP cores. This section provides an overview of what to consider in such instances.

For more information, refer to the *Stratix III Device Handbook* and the relevant IP user guides.

Altera recommends that you create an example top-level design with the desired pin outs and all interface IP instantiated, which enables the Quartus II software to validate your design and resource allocation before PCB and schematic sign off.

As the structure of memory controllers varies considerably, this section uses the ALTMEMPHY architecture, where appropriate.

## Bandwidth

Before designing any memory interface, determine the required bandwidth of the memory interface. Bandwidth can be expressed as:

Bandwidth = data width (bits) × data rate transfer (1/s) × efficiency

Data rate transfer  $(1/s) = 2 \times$  frequency of operation

After calculating the bandwidth requirements of your system, determine which memory type and device to use. Altera has a memory selection white paper, which highlights the differences between the memory types.

For information about selecting the different memory types, refer to the *Selecting the Right High-Speed Memory Technology for Your System* white paper.

DRAM typically has an efficiency of around 70%, but when using the Altera memory controller efficiency can vary from 10 to 92%.

•••

For information on DDR and DDR2 SDRAM efficiency, refer to *The Efficiency of the DDR & DDR2 SDRAM Controller Compiler* white paper.

In addition, Altera's FPGA devices support various data widths for different memory interfaces. The memory interface support between density and package combinations differs, so you must determine which FPGA device density and package combination best suits your application.

For information about the FPGA density and package support for the different memory types, refer to the *External Memory Interfaces in Stratix III Devices* chapter of the *Stratix III Device Handbook*.

## Full or Half Rate SDRAM Controller

When implementing memory controllers consider whether a half-rate or a full-rate datapath is optimal for your design. Full or half-rate mode have the following definitions:

- Full-rate mode presents data to the local interface at twice the width of the actual SDRAM interface at the full SDRAM clock rate

- Half-rate mode presents data to the local interface at four times the width of the actual SDRAM interface at half the SDRAM clock rate

Implementing memory controllers in half-rate mode results in the highest possible SDRAM clock frequency, while allowing the more complex core logic to operate at half this frequency. This implementation is most useful when core HDL designs are difficult to implement at the higher SDRAM clock frequency, but the required SDRAM bandwidth per I/O pin is still quite high.

However, controller operations are faster in full-rate mode with the IP operating at the same clock frequency as your system.

Consider that DDR devices can have a number of banks open at once. Each bank has a currently selected row. Changing the column within the selected row of an open bank requires no additional bank management commands to be issued. Changing the row in an active bank, or changing the bank both incur a protocol penalty that requires the precharge (PCH) command closes the active row or bank, and the active (ACT) command opens (or activates) the new row or bank combination. The duration of this penalty is a function of the controller clock frequency, the memory clock frequency, and the memory device characteristics. Calculating the impact of a change of memory and controller configuration on a given system is not a trivial task, as it depends on the nature of the accesses that are performed.

In this example each command takes a single clock cycle in a full-rate controller, but two clock cycles in a half-rate controller. The bank is not available for the subsequent ACT command until  $(t_{RP})$  after the PCH. So while the issuing of commands can be slower using a half-rate controller, the respective memory timing parameters remain the same.

Hence when a memory controller is used in half-rate mode, the control circuitry is clocked at half rate and so control operations are slower than in full-rate mode. However, the memory's clock frequency and physical properties are not affected.

Half-rate memory controllers always require at least one extra clock resource, half-rate system clock, in addition to the number of full-rate clocks that are required by default.

## PLL and Clock Usage

The exact number of clocks and hence PLLs required in your design depends greatly on the memory interface frequency, and the IP used.

You can build simple DDR slow-speed interfaces that typically require only two clocks: system and write. You can then use the rising and falling edges of these two clocks to derive four phases (0, 90, 180, and 270°).

However, as clock speeds increase, the timing margin decreases and additional clocks are required, to optimize setup and hold and meet timing. Typically, the following dedicated clocks may be required: resynchronization, and address and command.

Stratix III IOE includes dedicated circuitry for postamble protection, which is derived directly from the resynchronization clock.

In addition, some memory controller designs, like the ALTMEMPHY megafunction, use a VT tracking clock to measure and compensate for VT changes and their effects.

Half-rate memory controllers also require an additional half-rate system clock.

Consider the following points:

- PLLs in Stratix III devices connect to four maximum global clock nets.

- Top or bottom PLLs in Stratix III devices connect to ten maximum regional clock nets.

- Left or right PLLs in Stratix III devices connect to six maximum regional clock nets.

- EP3S...80 and larger devices have two PLLs located in the middle of each side of the device.

- EP3S...200 and larger device additionally have corner PLLs, which connect to six regional clock nets only.

- Dual regional clock nets are created by using a regional clock net from each region. For example, a single dual regional clock net uses two regional clock nets.

- If the design uses a dedicated PLL to only generate a DLL input reference clock, the PLL mode must be set to No Compensation, or the Quartus II software forces this setting automatically.

- If the design cascades PLLs, the source (upstream) PLL should have a low-bandwidth setting, while the destination (downstream) PLL should have a high-bandwidth setting.

- In Stratix III devices, two PLLs may be cascaded to each other through the clock network. In addition, where two PLLs exist adjacent to each other, there is a direct connection between them that does not require the global clock network. Using this path reduces clock jitter when cascaded PLLs. Cascaded PLLs are not recommended for ALTMEMPHY-based designs.

- You can only cascade PLLs between adjacent PLLs on the same side of the device.

- If PLLs are cascaded in ALTMEMPHY based designs, you must use the adjacent PLL (direct connection) method.

- Input and output delays are only fully compensated for, when the dedicated clock input pins associated with that specific PLL are used as its clock source.

- If the clock source for the PLL is not a dedicated clock pin for that specific PLL, jitter is increased, timing margin suffers, and the design may require an additional global or regional clock.

The following additional ALTMEMPHY-specific points apply:

ALTMEMPHY megafunctions require one global or regional clock, and five regional clock nets in Stratix III devices. Hence six clocks in total are required.

- Any PLL on any side of a Stratix III device can support a single ALTMEMPHY interface. Ideally, you should pick a PLL and a PLL input clock pin that are located on the same side of the device as the memory interface pins.

- As each PLL can only connect to four global clock nets, while the ALTMEMPHY megafunction requires six clock nets, an ALTMEMPHY-based design cannot cross from one side of a Stratix III device to the other side. For example, an ALTMEMPHY-based design can only exist within a dual regional side of a Stratix III device.

- If a single ALTMEMPHY interface spans two side quadrants, a middle side PLL must be the source for that interface. The ten dual region clocks that the single interface requires block the design using the adjacent PLL (if available) for a second interface.

- If a single ALTMEMPHY interface spans two top or bottom quadrants, a middle top or bottom PLL must be the source for that interface. The ten dual region clocks that the single interface require should not block the design using the adjacent PLL (if available) for a second interface.

For more information on clock networks, refer to *Clock Networks and PLLs in Stratix III Devices* in the *Stratix III Device Handbook*.

For more information on multiple memory controllers, refer to *AN* 462: Implementing Multiple Memory Interfaces Using the ALTMEMPHY Megafunction.

## DLL Usage and Sharing

DDR and DDR2 SDRAM interfaces in Stratix III devices use DQS phaseshift circuitry for data capture. All Stratix III devices include a total of four DLLs: one located in each corner of the device. Each DLL can support two different phase offsets, and each DLL can access the two sides adjacent to its location. Hence, there are opportunities for DLL sharing or multiple different memory interface types on a single side of a Stratix III device.

DLL reference clocks must come from either dedicated clock input pins located on either side of the DLL or from specific PLL output clocks. Any clock running at the memory frequency is valid for the DLLs.

For more information on DLLs, refer to the *External Memory Interfaces* chapter in the *Stratix III Device Handbook*.

To minimize the number of clocks routed directly on the PCB, typically this reference clock is sourced from the memory controllers PLL. In general, DLLs can use the PLLs directly adjacent to them (corner PLLs when available) or the closest PLL located in the two sides adjacent to its location. When designing for 780-pin packages with SE80, SE110 and SL150 devices, the PLL to DLL reference clock connection is limited.

Figure 7 shows the 780-pin package devices PLL and DLL reference clock connections. DLL3 is isolated from a direct PLL connection and can only receive a reference clock externally from pins clk[11:4]p.

Figure 7. PLL and DLL Reference Clock Connections in 780-pin Package Devices

The DLL reference clock should be the same frequency as the memory interface, but the phase is not important.

The required DQS capture phase is optimally chosen based on operating frequency and external memory interface type (DDR, DDR2, DDR3, QDRII, or RLDRAM II). As each DLL supports two possible phase offsets, two different memory interface types operating at the same frequency can easily share a single DLL. More may be possible, depending on the phase shift required.

Altera memory IP always specifies a default optimal phase setting, to override this setting, refer to the respective IP user guide.

To simplify the interface to core IP connections, multiple memory interfaces operating at the same frequency usually share the same system and static clocks as each other where possible. This sharing minimizes the number of dedicated clock nets required and reduces the number of different clock domains found within the same design.

As each DLL can directly drive four banks, but each PLL only has complete C (output) counter coverage of two banks (using dual regional networks), situations can occur where a second PLL operating at the same frequency is required. As cascaded PLLs increase jitter and reduce timing margin, you are advised to first ascertain if an alternative second DLL and PLL combination is not available and more optimal.

## Top, Bottom, Left, Right, and Hybrid Device Sides

This section discusses how to determine which device side to use (top and bottom, left and right, and hybrid).

## Top or Bottom and Left or Right Interfaces

Ideally any interface should wholly reside in a single bank. However, interfaces that span multiple adjacent banks or the entire side of a device are also fully supported. Although vertical and horizontal timing parameters are not identical, timing closure can be achieved on all sides of the FPGA for the maximum interface frequency.

## **Hybrid Interfaces**

The PLL regional clock net restriction and the fact that each DLL can drive its two adjacent sides suggests that an optimal PLL, DLL, and memory interface configuration resides in a single quadrant spanning two adjacent sides of the device. For maximum performance, Altera recommends that data groups for external memory interfaces should ideally reside within a single bank, but always within the same side of a device. High-speed memory interfaces in top or bottom versus left or right IOE have different timing characteristics and timing margins are affected. However, Altera can support interfaces with hybrid data groups that wrap around a corner of the device between vertical and horizontal I/O at some speeds (see Table 6)

| Table 6. Hybrid Memory Interface Speeds (Half Rate) Notes (1) through (4) |        |     |  |

|---------------------------------------------------------------------------|--------|-----|--|

| Memory Type Speed Grade f <sub>MAX</sub> (MHz)                            |        |     |  |

| DDR2 SDRAM                                                                | -2     | 300 |  |

|                                                                           | -3     | 267 |  |

|                                                                           | -4 (5) | 267 |  |

| DDR SDRAM                                                                 | -2     | 200 |  |

|                                                                           | -3     | 200 |  |

|                                                                           | -4 (5) | 200 |  |

#### Notes to Table 6:

- (1) Numbers are preliminary until characterization is final. The supported operating frequencies listed here are memory interface maximums for the FPGA device family. Your design's actual achievable performance is based on design and system specific factors, and static timing analysis of the completed design.

- (2) Applies for both DIMMS and components.

- (3) For the Quartus II version 8.0 hybrid functionality is not allowed and you see the following fitter error:

"Error: Cannot place DQ I/O "mem\_dq[nn]" to I/O location Pin\_Nn since its memory interface I/O group cannot be placed"

- (4) The Quartus II version 8.0 SP1 includes native support for hybrid interfaces at these rates.

- (5) At 1.1-V core voltage, the -4L speed grade devices have the same performance as the -4 speed grade devices.

## DQ and DQS Width Limits

Stratix III device do not limit the width of DDR or DDR2 SDRAM interfaces beyond the following requirements:

- The entire interface DQ and clock and address signals should reside within the same bank or side of the device.

- Maximum possible interface width in any particular device is limited by the number of DQS groups available within that bank or side, see Table 5.

- Sufficient regional clock networks are available to the interface PLL to allow implementation within the required number of quadrants.

- Sufficient spare pins exist within the chosen bank or side of the device to include all other address and command, and clock pin placement requirements.

- The greater the number of banks, the greater the skew, hence Altera recommends that you always generate a test project of your desired configuration and confirm that it meets timing.

## Address and Command, Clock, and Other Signals

This section describes the following signals:

- Address and command

- Clock

- Other signals

#### **DDR SDRAM Component Additional Pins**

The largest individual DDR SDRAM components typically available are  $1 \text{ GB} \times 4$  devices. These devices usually require a maximum of 29 pins, which can be broken down in the following way:

- 4 DQ pins

- 1 DM pin

- 1 DQS pin

- 14 A[13:0] pins

- 2 BA[1:0]pins

- 2 CK and CK# pins

- 5 CKE, CS#, RAS#, CAS#, WE# pins

DQ, DM, and DQS should reside in a dedicated ×4 DQS group, the remaining 23 additional signals should be placed within the same bank.

#### **DDR SDRAM DIMM Additional Pins**

The largest DDR SDRAM DIMMs typically available are 2 GB  $\times$ 72 dual rank modules. These modules usually require a maximum of 119 pins, which can be broken down in the following way:

- 72 DQ pins

- 9 DM[8:0] pins

- 9 DQS[8:0]pins

- 14 A[13:0]pins

- 2 BA[1:0]pins

- 6 CK and CK#[2:0] pins

- 7 CKE[1:0], CS#[1:0], RAS#, CAS#, WE# pins

DQ, DM, and DQS should reside in 9 ×8 DQS groups ensuring that DQ group pin order is maintained. The remaining 29 additional signals should be placed within the same bank or side of the device.

ALTMEMPHY-based interfaces do not directly support dual rank implementations.

#### **DDR2 SDRAM Component Additional Pins**

The largest individual DDR2 SDRAM components typically available are 1 GB  $\times$ 4 devices. These devices usually require a maximum of 32 pins, which can be broken down in the following way:

- 4 DQ pins

- 1 DM pins

- 2 DQS and DQSn pins

- 14 A[13:0] pins

- 3 BA[2:0]pins

- 2 CK and CK# pins

- 5 CKE, CS#, RAS#, CAS#, WE# pins

- 1 ODT pin

DDR2 SDRAM has additional ODT and DQSn signals compared with DDR SDRAM. Stratix III ×4 DQS groups support either DQSn or DM, but not both. Additional DM pins can be placed in spare DDIO pin located within the same bank (to minimize skew), if you do not require leveling delay chains.

ALTMEMPHY- based interfaces do not support both differential DQS mode and DM in a  $\times$ 4 configuration.

DQ, DQS, and DQSn (and DM) should reside in a dedicated ×4 DQS group. The remaining 25 or 26 (with DM) additional signals should be placed within the same bank.

Future 2 GB and 4 GB devices will require A14 and A15 signal connectivity.

#### **DDR2 SDRAM DIMM Additional Pins**

The largest DDR2 SDRAM DIMMs typically available are 4 GB ×72 dual rank modules. These modules usually require a maximum of 132 pins, which can be broken down in the following way:

- 72 DQ pins

- 9 DM[8:0]pins

- 9 DQS[8:0]pins

- 9 DQSn[8:0] pins

- 15 A[14:0] pins

- 3 BA[2:0] pins

- 6 CK and CK#[2:0] pins

- 7 CKE0[1:0], CS#[1:0], RAS#, CAS#, WE# pins

- 2 ODT[1:0] pins

DQ, DM, and DQS and DQSn should reside in  $9 \times 8$  DQS groups ensuring that DQ group pin order is maintained. The remaining 33 additional signals should be placed within the same bank or side of the device.

#### **RUP and RDN Calibration Blocks**

If calibrated series, parallel, or dynamic termination is used for the I/O in your design, your design requires a calibration block. This block requires a pair of RUP and RDN pins located within the same  $V_{CCIO}$  voltage bank.

This calibration block is not required to be within the same bank or side of the device as the IOEs it is serving. However, RUP and RDN pins are typically shared with DQ and DQS pins in Stratix III devices.

DQS and DQSn pins in some of the ×4 groups can also be used as RUP and RDN pins. You cannot use a ×4 group for memory interfaces if you are using its pin members as RUP and RDN pins for OCT calibration. You may use the  $\times 8/\times 9$  group that includes this  $\times 4$  group, if either of the following conditions apply:

- You are not using DM pins with your differential DQS pins

- You are not using complementary or differential DQS pins

A  $\times$ 8/ $\times$ 9 group comprises 12 pins, as the groups are formed by stitching two groups of  $\times$ 4 mode with 6 total pins each. A typical  $\times$ 8 or  $\times$ 16 DDR2 SDRAM device consists of one DQS, one DM, and 8 DQ pins, which totals 10 pins. So if you choose your pin assignment carefully, you can use the 2 extra pins for RUP and RDN.

If you are using both DM and differential DQS modes at the same time, pick different pin locations for RUP and RDN pins—for example, in the bank that contains address and command pins.

You need to pick your DQS and DQ pins manually for the ×8, ×16 and ×18, or ×32 and ×36 groups, if they have pins they are using for RUP and RDN. The Quartus II software may not place these pins correctly and may give you a no-fit.

For more information on calibration blocks, refer to *Stratix III Device I/O Features* chapter in the *Stratix III Device Handbook*, the *ALTOCT Megafunction User Guide*, and *AN* 465: *Implementing OCT Calibration in Stratix III Devices*.

ALTMEMPHY-based interfaces do not directly support dual rank implementations.

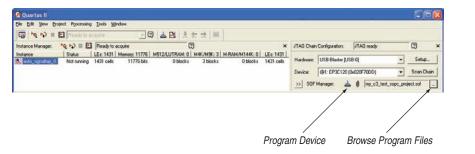

## Instantiate PHY and Controller in a Quartus II Project

After selecting the appropriate device and memory type, create a project in the Quartus<sup>®</sup> II software that targets the device and memory type.

When instantiating the datapath for DDR and DDR2 SDRAM interfaces in Stratix III devices, Altera recommends that you use the ALTMEMPHY megafunction for the datapath and PHY. The ALTMEMPHY megafunction features a license-free PHY that you may use with the Altera SDRAM high-performance controllers or your own custom controller.

The Altera high-performance controllers automatically include the ALTMEMPHY megafunction. Even if you plan to use your own controller, Altera recommends that you first create a design using a SDRAM high-performance controller and then replace the Altera controller with your own controller. This method gives you an example design, which you can simulate and verify on your own PCB.

For more information about instantiating the PHY, refer to the *External* DDR Memory PHY Interface (ALTMEMPHY) Megafunction User Guide.

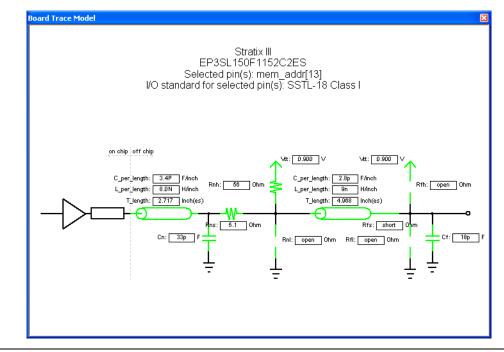

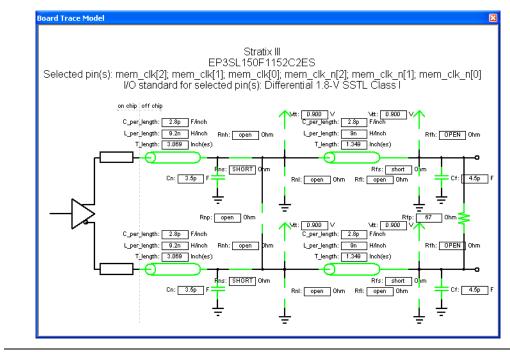

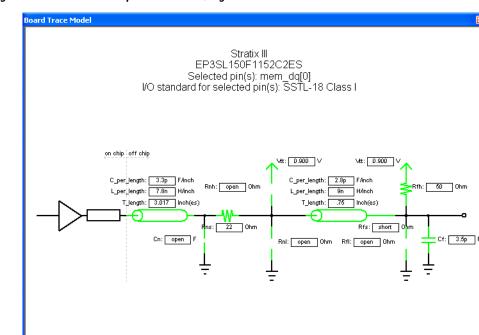

## Perform Board-Level Simulations and Line Simulation

This design flow indicates that you determine board design constraints and perform board-level simulations at the end of the flow. However, Altera recommends prelayout SI simulations (line simulations) should take place before board layout and that you use these parameters and rules during the initial design development cycle. Advanced I/O timing and board trace models now directly impact device timing closure.

## **Add Constraints**

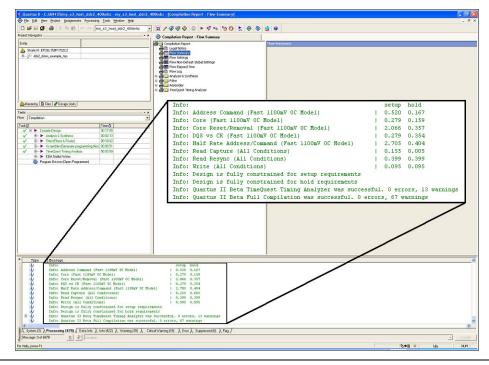

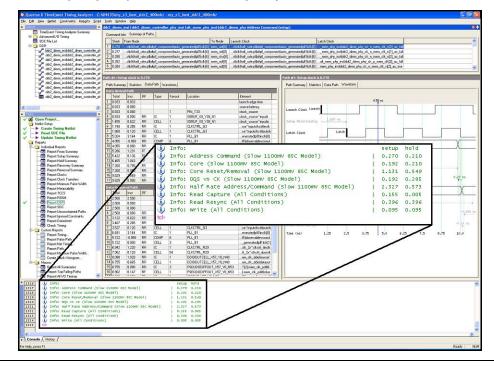

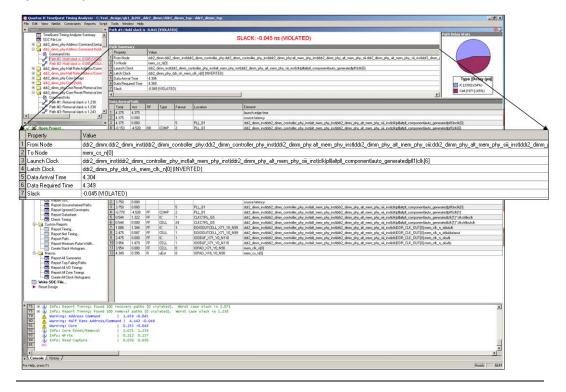

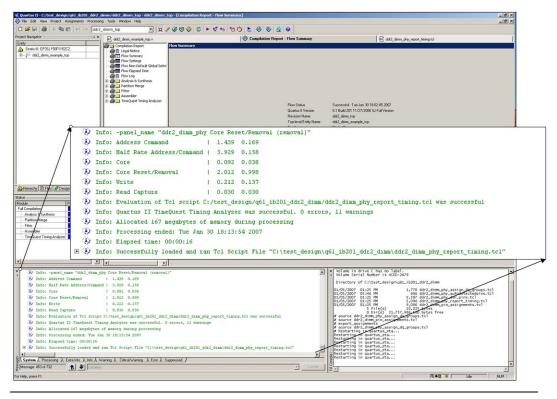

The next step in the design flow is to add the timing, location, and physical constraints related to the external memory interface. These constraints include timing, pin locations, I/O standards, and pin loading assignments. The ALTMEMPHY megafunction only supports timing analysis using the TimeQuest Timing Analyzer with Synopsys Design Constraints (.sdc) assignments. These constraints are derived from the parameters you entered for the ALTMEMPHY megafunction or the SDRAM high-performance controller, based on the DDR2 and DDR SDRAM data sheet and tolerances from the board layout. The ALTMEMPHY megafunction uses TimeQuest timing constraints and the timing driven fitter to achieve timing closure. After instantiating the ALTMEMPHY megafunction, the ALTMEMPHY MegaWizard generates the following files that you need to properly constrain the design:

- <variation\_name>\_phy\_ddr\_timing.sdc to set timing constraints

- *<variation\_name>\_pin\_assignments.tcl* to add I/O standard setting assignments

- <variation\_name>\_phy\_assign\_dq\_groups.tcl to add the DQ group assignments to relate the DQ and DQS pin groups together for the Quartus II fitter to place them correctly