# Xilinx FPGA Dynamic Probe

**Online Help**

### Notices

© Agilent Technologies, Inc. 2001-2009

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

### **Trademarks**

Microsoft®, MS-DOS®, Windows®, Windows 2000®, and Windows XP® are U.S. registered trademarks of Microsoft Corporation.

Adobe®, Acrobat®, and the Acrobat Logo® are trademarks of Adobe Systems Incorporated.

### **Manual Part Number**

Version 03.82.0000

### **Edition**

April 10, 2009

Available in electronic format only

Agilent Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

### **Safety Notices**

### CAUTION

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

### **Using the Xilinx FPGA Dynamic Probe**

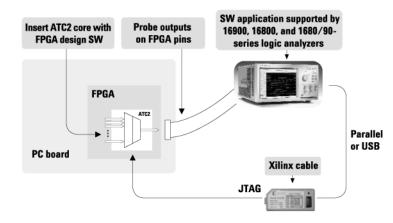

When an Agilent ATC2 or MTC trace core has been inserted into an FPGA, the FPGA dynamic probe lets a logic analyzer capture data from signals inside the FPGA.

| ATC2 | The Agilent Trace Core (see page 9) lets you view a large number of internal FPGA signals using a small number of pins while consuming minimal FPGA resources (just over 1 slice required per input signal to ATC2). With ATC2 cores, the FPGA dynamic probe lets you change probe points without recompiling or affecting the timing of the design.                                                                                                       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MTC  | The MicroBlaze Trace Core (see page 11) lets you capture and decode the execution of a MicroBlaze soft processor core inside an FPGA. With 2x pin compression and the ability to look at just the significant signals, you can debug using fewer pins. The E9524A MicroBlaze trace toolset provides inverse assembly mnemonics in the Listing window, and you can view the high-level source code associated with captured execution in the Source window. |

With either core, the FPGA dynamic probe's automatic pin-mapping and ability to import internal signal names from the FPGA design tools makes setting up the logic analyzer easy.

- Probing FPGA Debug Pins (see page 13)

- Installing and Licensing the FPGA Dynamic Probe (see page 15)

- ATC2 Design Steps (see page 17)

- ATC2 Design Step 1. Determine the ATC2 core parameters (see page 18)

- ATC2 Design Step 2. Create the ATC2 core (see page 21)

- ATC2 Design Step 3. Select groups of signals to probe (see page 22)

- MTC Design Steps (see page 23)

- MTC Design Step 1. Create and instantiate an MTC core (see page 24)

- MTC Design Step 2. Implement your Xilinx FPGA design with MicroBlaze and MTC cores in place (see page 25)

- Measurement Steps (see page 27)

- Measurement Step 1. Establish connection between analyzer and ATC2 or MTC core (see page 28)

- Measurement Step 2. Download configuration bits into FPGA (see page 31)

- Measurement Step 3. Map FPGA pins (see page 32)

- Measurement Step 4. Import signal names (see page 37)

- Measurement Step 5. Adjust sampling positions for state (synchronous) cores (see page 41)

- Measurement Step 6. Make the measurement (see page 44)

- Troubleshooting (see page 49)

- Concepts (see page 55)

- Reference (see page 63)

- FPGA Dynamic Probe Setup Dialog (see page 64)

- FPGA Dynamic Probe Bank Selection Dialog (see page 71)

- Specifications and Characteristics (see page 73)

- **See Also** Probe Control, COM Automation (see page 77)

- Probe Setup, XML Format (see page 79)

### Contents

Using the Xilinx FPGA Dynamic Probe 3

- **1** Agilent Trace Core (ATC2) Overview

- 2 MicroBlaze Trace Core (MTC) Overview

- **3** Probing FPGA Debug Pins

- **4** Installing and Licensing the FPGA Dynamic Probe

### 5 ATC2 Design Steps

ATC2 Design Step 1. Determine ATC2 core parameters18State (Synchronous) vs. Timing (Asynchronous) Cores18Number of FPGA Debug Pins, Number of Banks19FPGA Resource Consumption20

ATC2 Design Step 2. Create the ATC2 core 21

ATC2 Design Step 3. Select groups of signals to probe 22

### 6 MTC Design Steps

MTC Design Step 1. Create and instantiate an MTC core 24

MTC Design Step 2. Implement your Xilinx FPGA design with MicroBlaze and MTC cores in place 25

### 7 Measurement Steps

Measurement Step 1. Establish connection between analyzer and ATC2 or MTC core 28

Measurement Step 2. Download configuration bits into FPGA 31

Measurement Step 3. Map FPGA pins 32

To map pins for cores with auto pin-mapping 32

To map pins for cores without auto pin-mapping 34

Measurement Step 4. Import signal names 37

To trim imported bus/signal names 38

To rename imported bus/signal names 38

To define additional FPGA bus/signal names 39

Measurement Step 5. Adjust sampling positions for state (synchronous) cores 41

| Measurement Step 6. Make the measurement | 44 |

|------------------------------------------|----|

| Making Measurements with ATC2 Cores      | 44 |

| Making Measurements with MTC Cores       | 46 |

### 8 FPGA Dynamic Probe Troubleshooting

If you don't see activity in the logic analyzer 50

If state mode measurements don't work 51

If the ATC2 or MTC core isn't present in an FPGA after downloading configuration bits 52

If you get the "Can not open cable" error message 53

### **9 FPGA Dynamic Probe Concepts**

How do ATC2 cores affect design timing and signal routing? 56

How do ATC2 cores affect FPGA performance? 57

Can I put multiple ATC2 cores in a single device? 58

Should I leave the ATC2 core in my design after validation is complete? 59

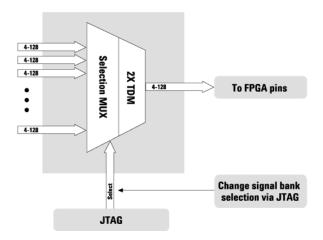

How does the optional 2X pin compression technology work? 60

Automated Logic Analyzer Set Up 61

How do I define buses/signals created in FPGA Editor? 62

### **10 FPGA Dynamic Probe Reference**

FPGA Dynamic Probe Setup Dialog 64 **Cable Connection Dialog** 65 Pin Mapping Dialog 66 Pin Mapping Edit Dialog 67 Select FPGA Configuration File Dialog 68 Select Signal Import File Dialog 69 **Properties Dialog** 69 Core Details Dialog 70 FPGA Dynamic Probe Bank Selection Dialog 71 Trim Bus/Signal Names Dialog 71 FPGA Dynamic Probe Specifications and Characteristics 73

### **11 Probe Control, COM Automation**

### 12 Probe Setup, XML Format

<Assignment> Element 80

<ATC\_II> Element 81

<Bank> Element 82 <Banks> Element 86 <Cable> Element 87 <Core> Element 88 <Cores> Element 90 <DefinedProbes> Element 91 <Device> Element 92 <Devices> Element 94 <JTAG\_Chain> Element 96 <Label> Element 97 <Label> Element (under NonATCLabels) 98 <Labels> Element 99 <NonATCLabels> Element 100 <PinMapping> Element 101 <Pod> Element 103 104 <Pods> Element <Probe> Element 105 <Properties> Element 106 <Signal> Element (under Bank) 108 <Signal> Element (under Probe) 109 <Signals> Element (under Bank) 110 <Signals> Element (under Probe) 112 <SymbolInfo> Element 113 <TriggerInfo> Element 114 <WindowInfo> Element 115

### Index

Xilinx FPGA Dynamic Probe Online Help

# Agilent Trace Core (ATC2) Overview

When used with Agilent ATC2 cores, the FPGA dynamic probe lets you:

• View internal activity.

With a logic analyzer, you are normally limited to measuring signals at the periphery of the FPGA. With the FPGA dynamic probe, you can now access signals internal to the FPGA. You can measure up to 64 internal signals for each external pin dedicated to debug, unlocking visibility into your design that you never had before.

• Make multiple measurements in seconds.

Moving probe points internal to an FPGA used to be time consuming. Now, in less than a second you can easily measure a different set of internal signals – without design changes – and FPGA timing stays constant when you select new sets of internal signals for probing.

• Leverage the work you did in your design environment.

The FPGA dynamic probe is the industry's first tool that maps internal signal names from your FPGA design tool to your logic analyzer. Eliminate unintentional mistakes and save hours of time with this automatic setup of signal and bus names on your logic analyzer.

Create a time saving FPGA measurement system. Insert an ATC2 (Agilent Trace Core) core into your FPGA design. With the application running on your logic analyzer via JTAG you control which group of internal signals to measure.

### **1** Agilent Trace Core (ATC2) Overview

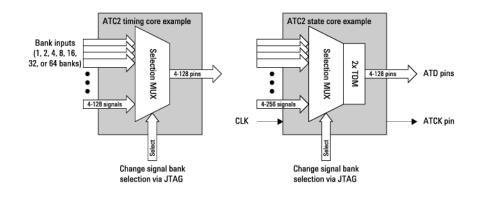

Access 64 internal signals for each debug pin. Select cores with 1, 2, 4, 8, 16, or 32 signal banks. Signal banks all have identical width (4 to 128 signals wide) determined by the number of pins you devote for debug. Each pin provides sequential access to 1 signal on every input bank. Using an optional 2X time division compression in state mode, each pin can simultaneously access 2 signals per bank.

Xilinx FPGA Dynamic Probe Online Help

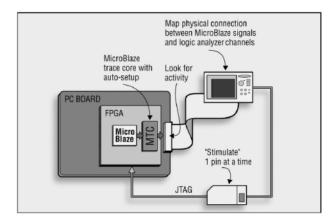

# MicroBlaze Trace Core (MTC) Overview

When used with Agilent MTC cores, the FPGA dynamic probe lets you:

• View internal MicroBlaze signals with minimal impact on the timing of your design.

MTC cores are designed to be very small in terms of device resource consumption. An MTC core in a XC2V3000 device consumes roughly 1% of the LUTs and flops.

• Use 2x pin compression to reduce the number of FPGA pins required.

How does the optional 2X pin compression technology work? (see page 60)

• Use automatic pin-mapping to reduce logic analyzer set up time.

Agilent's MTC reduces the set up time for an initial trace measurement. You can literally connect a logic analyzer to a connector with MTC core outputs routed to it, and within seconds, the logic analyzer becomes ready to take a MicroBlaze trace measurement.

### 2 MicroBlaze Trace Core (MTC) Overview

Xilinx FPGA Dynamic Probe Online Help 3 Probing FPGA Debug Pins

The supported mechanisms for probing the FPGA debug pins with a logic analyzer are: soft touch (34-channel or 17 channel), Mictor, Samtec, and flying lead probes.

For more information on probing, see "Probing the Device Under Test" (in the online help).

### Probing FPGA Debug Pins

Xilinx FPGA Dynamic Probe Online Help

4

# Installing and Licensing the FPGA Dynamic Probe

Before you can use the Agilent B4655A Xilinx FPGA dynamic probe or E9524A MicroBlaze trace toolset, you must install and license the software:

- 1 Install the FPGA dynamic probe software from the application software CD or from the Agilent web site at: "http://www.agilent.com/find/la-sw-download"

- **2** Follow the instructions on your entitlement certificate to redeem and install the software licenses.

### 4 Installing and Licensing the FPGA Dynamic Probe

**Xilinx FPGA Dynamic Probe Online Help**

# 5 **ATC2 Design Steps**

Before you can use the FPGA dynamic probe software with the Agilent Logic Analyzer application, you must take these design steps:

- 1 Determine the ATC2 core parameters (see page 18)

- State (Synchronous) vs. Timing (Asynchronous) Cores (see page 18)

- Number of FPGA Debug Pins, Number of Banks (see page 19)

- FPGA Resource Consumption (see page 20)

- **2** Create the ATC2 core (see page 21)

- **3** Select groups of signals to probe (see page 22)

- See Also • For more ATC2 design information, see: "http://www.agilent.com/find/fpga"

- How do ATC2 cores affect design timing and signal routing? (see page 56)

- How do ATC2 cores affect FPGA performance? (see page 57)

- Can I put multiple ATC2 cores in a single device? (see page 58)

- Measurement Steps (see page 27)

### ATC2 Design Step 1. Determine ATC2 core parameters

Before you use Xilinx ChipScope Pro to insert the ATC2 core and select groups of signals to probe, you need to determine the ATC2 core parameters you will use.

- State (Synchronous) vs. Timing (Asynchronous) Cores (see page 18)

- Number of FPGA Debug Pins, Number of Banks (see page 19)

- FPGA Resource Consumption (see page 20)

- **Next** ATC2 Design Step 2. Create the ATC2 core (see page 21)

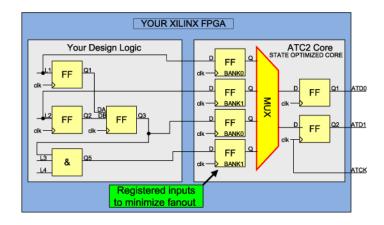

### State (Synchronous) vs. Timing (Asynchronous) Cores

State cores:

- Provide most-accurate measurements for functional debug in one time domain.

- Register inputs to minimize fan out.

- Support time division multiplexing for 2X pin reduction (see page 60).

- Support calibration for more accurate measurements on buses with narrow data valid windows.

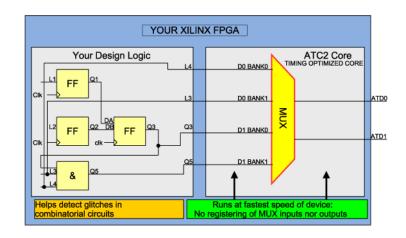

Timing cores:

- Are best for measurements across multiple time domains.

- Run at fastest-possible speed of device, no registering of MUX inputs or outputs.

- Have minimal impact on design timing.

The FPGA dynamic probe will detect the type of ATC2 core and automatically set up the appropriate logic analyzer sampling mode (see page 61).

### Number of FPGA Debug Pins, Number of Banks

Using the FPGA dynamic probe, each pin provides access to up to 64 internal signals. The number of debug pins can range from 4 to 128 depending on your needs. When using state (synchronous) cores, one additional pin is used for the clock.

| Number<br>of debug                                           | Maximum number of internal FPGA signals that can be probed (w/2x TDM <sup>2</sup> ) per number of banks |         |         |          |           |           |               |  |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------|---------|----------|-----------|-----------|---------------|--|

| <b>pins<sup>1</sup></b><br>(4-128 in<br>incremen<br>ts of 1) | 1 bank                                                                                                  | 2 banks | 4 banks | 8 banks  | 16 banks  | 32 banks  | 64 banks      |  |

| 4                                                            | 4 (8)                                                                                                   | 8 (16)  | 16 (32) | 32 (64)  | 64 (128)  | 128 (256) | 256 (512)     |  |

| 8                                                            | 8 (16)                                                                                                  | 16 (32) | 32 (64) | 64 (128) | 128 (256) | 256 (512) | 512<br>(1024) |  |

| 16  | 16 (32)   | 32 (64)   | 64 (128)      | 128 (256)      | 256 (512)      | 512<br>(1024)  | 1024<br>(2048)  |

|-----|-----------|-----------|---------------|----------------|----------------|----------------|-----------------|

| 32  | 32 (64)   | 64 (128)  | 128 (256)     | 256 (512)      | 512<br>(1024)  | 1024<br>(2048) | 2048<br>(4096)  |

| 64  | 64 (128)  | 128 (256) | 256 (512)     | 512<br>(1024)  | 1024<br>(2048) | 2048<br>(4096) | 4096<br>(8192)  |

|     |           |           |               |                |                |                |                 |

| 128 | 128 (256) | 256 (512) | 512<br>(1024) | 1024<br>(2048) | 2048<br>(4096) | 4096<br>(8192) | 8192<br>(16384) |

<sup>1</sup> When using state (synchronous) cores, one extra pin is required for the clock.

$^2$  The maximum number of signals per bank doubles when 2x TDM is selected. 2x TDM is only available for state cores.

### **FPGA Resource Consumption**

Each input signal adds roughly 1 slice to the size of the ATC2 core. The ATC2 cores have been designed to be as small as possible. For example, an ATC2 state core configured with 8 signal banks and 80 signals per bank consumes about 94 slices, or less than 1 percent of the resources on a Xilinx XCV2000 device.

The actual core size depends on the parameters chosen, such as:

- 1 Core type: state, state with pin compression or timing.

- 2 Number of pins.

- **3** Number of signal banks.

Xilinx recommends measuring core sizes in terms of flops and LUTs because this is what the place and route tools work with. A calculator to determine LUT and flop resource utilization from the combination of the ATC2 core and ICON (JTAG controller) is available at "http://www.agilent.com/find/fpga" or in the Xilinx Core Inserter tool.

Why do I seeThe path from the probed signal to the output pad is not registered in the timing core?The path from the probed signal to the output pad is not registered in the timing core?The flip-flops in the timing core are used only for core control and status. An example of a core control signal is the bank mux select. These control and status flip-flops are registered by the JTAG TCK clock, not a design clock. Therefore, these flip-flops are part of the low-speed circuit used by the logic analyzer to control and poll the core.

### ATC2 Design Step 2. Create the ATC2 core

Use Xilinx ChipScope Pro or EDK (Embedded Development Kit) to create the ATC2 core and to merge it with your design. Using either of these tools, you can specify the parameters of the ATC2 core (number of pins, number of signal banks, state or timing measurement, and other ATC2 attributes), and you can specify which design signals go to the ATC2, making them available for real-time measurement.

ChipScope Pro includes Core Generator and Core Inserter.

Core Inserter Xilinx Core Inserter puts the core into your FPGA design post synthesis.

Core Inserter produces a .cdc file. This is a small file listing the signal inputs to the ATC2 core. This file is used to automatically synchronize design signal names with logic analysis bus and signal names.

Agilent recommends using Core Inserter so you can take advantage of signal-name mapping.

- Core Generator or<br/>EDKIf you use Core Generator or EDK, the tool instantiates your<br/>parameterized ATC2 as a black-box Verilog or VHDL unit. The synthesis<br/>tool puts the instantiated core into your design during the synthesis<br/>process. ATC2 cores produced by Core Generator are compatible with<br/>these synthesis tools:

- Exemplar Leonardo Spectrum

- Synopsys Design Compiler

- Synopsys Design Compiler II

- Synopsys FPGA Express

- Synplicity Synplify

- Xilinx XST 4

Xilinx has a stimulus core known as VIO. This core can only be created and placed in a design using Xilinx Core Generator. For a single design that contains both a VIO core and an ATC2, Core Generator must be used.

The Core Generator or EDK tools make a .cdc file that you can edit so that the bank input signal names reflect the signal path of the probed net. Otherwise, if no .cdc file is loaded, you can manually rename ATC signal names with the signal names from your design—the FPGA dynamic probe will remember these name changes.

**Next** • ATC2 Design Step 3. Select groups of signals to probe (see page 22)

### ATC2 Design Step 3. Select groups of signals to probe

Specify banks of internal signals that are potential candidates for logic analysis measurements (using Xilinx Core Inserter or Xilinx embedded development kit (EDK)).

• Measurement Step 1. Establish connection between analyzer and ATC2 core (see page 28)

Xilinx FPGA Dynamic Probe Online Help

## •• 6 MTC Design Steps

Before you can use the FPGA dynamic probe software (and the *Agilent Logic Analyzer* application) with MTC cores, you must take these design steps:

- 1 Create and instantiate an MTC core (see page 24)

- 2 Implement your Xilinx FPGA design with MicroBlaze and MTC cores in place (see page 25)

- See Also For more MTC design information, see: "http://www.agilent.com/find/microblaze"

- Measurement Steps (see page 27)

### MTC Design Step 1. Create and instantiate an MTC core

Use Xilinx Platform Studio to select the MTC core and specify the parameters that best match your design needs. Parameters include: data compression, status signals, and location.

• MTC Design Step 2. Implement your Xilinx FPGA design with MicroBlaze and MTC cores in place (see page 25)

# MTC Design Step 2. Implement your Xilinx FPGA design with MicroBlaze and MTC cores in place

Once the design is ready for prototyping in the FPGA, use the Xilinx tools to implement the design (generate the bitstream) including the MicroBlaze and MTC cores. You are then ready to set up the logic analyzer for measurement.

• Measurement Step 1. Establish connection between analyzer and ATC2 core (see page 28)

### 6 MTC Design Steps

Xilinx FPGA Dynamic Probe **Online Help**

### **Measurement Steps**

After you have completed the Design Steps (see page 17) of inserting the ATC2 core and selecting groups of signals to probe, you are ready to take these measurement steps in the Agilent Logic Analyzer application:

- 1 Establish connection between analyzer and ATC2 core (see page 28)

- **2** Download configuration bits into FPGA (see page 31)

- **3** Map FPGA pins (see page 32)

- 4 Import signal names (see page 37)

- **5** Adjust sampling positions for state (synchronous) cores (see page 41)

- 6 Make the measurement (see page 44)

- Making Measurements with ATC2 Cores (see page 44)

- Making Measurements with MTC Cores (see page 46)

# Measurement Step 1. Establish connection between analyzer and ATC2 or MTC core

The FPGA dynamic probe application establishes a connection between the logic analyzer and a Xilinx cable. It also determines what devices are on the JTAG scan chain and lets you pick which one you wish to communicate.

To establish a connection between the logic analyzer and the ATC2 or MTC core:

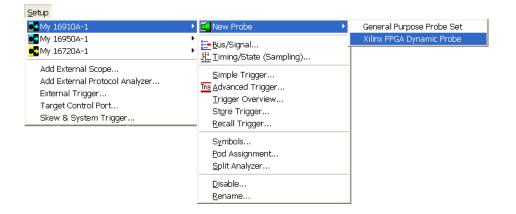

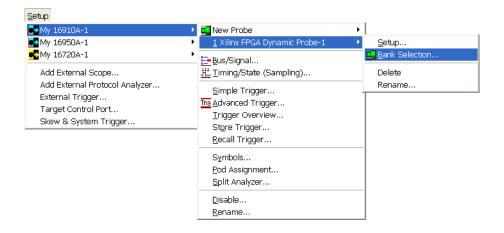

1 Add a new FPGA Dynamic Probe set by choosing Setup>(Logic Analyzer Module);>New Probe>Xilinx FPGA Dynamic Probe.

Or, in the Overview window, from a module's drop-down menu, choose New Probe>Xilinx FPGA Dynamic Probe.

| Modules           | Windows                                                 |

|-------------------|---------------------------------------------------------|

| Slot D            |                                                         |

| ₩y 16910A-1       | Listing-1                                               |

| New Probe         | General Purpose Probe Set     Xilinx FPGA Dynamic Probe |

| Add Connection    | Show                                                    |

| Delete Connectio  | n ·                                                     |

| Setup             |                                                         |

| Disable<br>Rename |                                                         |

|                   |                                                         |

2 In the FPGA Dynamic Probe Setup dialog (see page 64), click Cable Connection....

| FPGA Dynamic Probe Setup                     | X                              |

|----------------------------------------------|--------------------------------|

| Press "Cable Connection" to read JTAG chain. | Cable Connection               |

|                                              | Configure Device               |

|                                              | Pin <u>Mapping</u>             |

|                                              | <u> </u> K Cancel <u>H</u> elp |

**3** In the Cable Connection dialog (see page 65), select the type of cable and, if necessary, specify any cable parameters; then, click **OK**.

| Select type of cabl                                   | e             |

|-------------------------------------------------------|---------------|

| 💿 Xilinx Cable                                        |               |

| 🔿 No Cable (Demo                                      | ) Mode)       |

| Cable Server                                          |               |

| 🔾 Local Host                                          | 💿 Remote Host |

| Server Name: mt                                       | :x33          |

|                                                       |               |

|                                                       | ×             |

| Cable parameters<br>Cable type:<br>Parallel<br>Speed: | ▼<br>Port:    |

| Cable type:<br>Parallel                               | Port:         |

When the connection has been established, you will see the devices on the JTAG chain, and you can select the desired ATC2 or MTC core.

| PGA Dynamic Probe Se                                     | tup              |             |                                                                 |                                                                        |

|----------------------------------------------------------|------------------|-------------|-----------------------------------------------------------------|------------------------------------------------------------------------|

| On Device Core<br>Device 0 No Cores<br>Device 1 No Cores | Imported Signals | Pin Mapping | Details<br>XC18V00 - not configurable<br>XC2V250 - configurable | Cable Connection<br>Device 1<br>Configure Device<br>Import Bus/Signals |

| <                                                        |                  |             |                                                                 | <u>P</u> roperties<br>ncel <u>H</u> elp                                |

### 7 Measurement Steps

Next • Measurement Step 2. Download configuration bits into FPGA (see page 31)

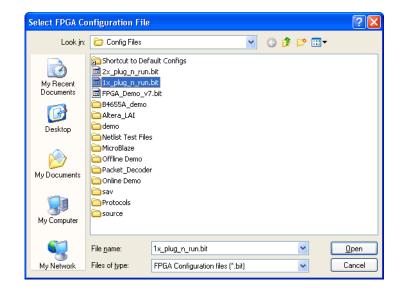

### Measurement Step 2. Download configuration bits into FPGA

To download configuration bits into an FPGA:

1 In the FPGA Dynamic Probe Setup dialog (see page 64), select the FPGA device to which you wish to download configuration bits; then, click **Configure Device...**.

| On | Device   | Core     | Imported Signals | Pin Mapping | Details                    | Cable Connection    |

|----|----------|----------|------------------|-------------|----------------------------|---------------------|

|    | Device 0 | No Cores |                  |             | XC18V00 - not configurable |                     |

|    | Device 1 | No Cores |                  |             | XC2V250 - configurable     | Device 1            |

|    |          |          |                  |             |                            | Configure Device    |

|    |          |          |                  |             |                            |                     |

|    |          |          |                  |             |                            | Import Bus/Signals. |

|    |          |          |                  |             |                            |                     |

|    |          |          |                  |             |                            |                     |

|    |          |          |                  |             |                            | Pin <u>M</u> apping |

|    |          |          |                  |             |                            |                     |

| <  |          |          |                  |             | >                          | Properties          |

- 2 In the Select FPGA Configuration File dialog (see page 68), select the FPGA configuration file; then, click **Open**.

- See Also If the ATC2 or MTC core isn't present in an FPGA after downloading configuration bits (see page 52)

- Next Measurement Step 3. Map FPGA pins (see page 32)

### **Measurement Step 3. Map FPGA pins**

Quickly specify how the FPGA pins (the signal outputs of ATC2 or MTC) are connected to your logic analyzer. Select your probe type and rapidly provide the information needed for the logic analyzer to automatically track names of signals routed through the ATC2 or MTC core.

To map FPGA pins to logic analyzer probes:

1 In the FPGA Dynamic Probe Setup dialog (see page 64), select the ATC2 or MTC core whose output pins you want to map; then, click **Pin Mapping...**.

| PGA I | Dynamic I            | Probe Setu | p                |             |                                                      | D                   |

|-------|----------------------|------------|------------------|-------------|------------------------------------------------------|---------------------|

| On    | Device               | Core       | Imported Signals | Pin Mapping | Details                                              | Cable Connection    |

|       | Device 0<br>Device 1 | No Cores   |                  |             | XC18V00 - not configurable<br>XC2V250 - configurable | Device 1            |

|       |                      | Core 0     | <none></none>    | Incomplete  | State, 64 banks, 9 pins                              | Configure Device    |

|       |                      |            |                  |             |                                                      | Import Bus/Signals  |

|       |                      |            |                  |             |                                                      | Core 0 Pin Mapping  |

|       |                      |            |                  |             |                                                      | Pin <u>M</u> apping |

| <     |                      |            |                  |             |                                                      | Properties          |

|       |                      |            |                  |             | <u> </u>                                             | ncel <u>H</u> elp   |

Your next steps depend on whether the core has auto pin-mapping capability:

- To map pins for cores with auto pin-mapping (see page 32)

- To map pins for cores without auto pin-mapping (see page 34)

### To map pins for cores with auto pin-mapping

1 If you have a core with auto pin-mapping (like the MTC or an ATC2 core with the auto setup parameter enabled), pin mapping happens automatically after you click **Pin Mapping...** (in the FPGA Dynamic Probe Setup dialog (see page 64)). When the automatic pin mapping completes, you see:

| Agilent | Logic Analyzer Question                                                                              |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2       | Successfully mapped all ATC pins!<br>Would you like to see a graphical view of how pins were mapped? |  |  |  |  |  |

|         | <u>⊻</u> es <u>N</u> o                                                                               |  |  |  |  |  |

# **NOTE** The FPGA Dynamic Probe does not know the correct reference designators; it simply uses J1, J2, etc.

Make sure that the reference designators are correct by looking at the graphical view and editing the probes that were automatically set up. (This is especially important if you will use the "Probe Summary tab" (in the online help) in the System Summary dialog for reconnecting the probes later.)

2 To see how pins were mapped, click Yes.

In the Pin Mapping dialog, you will see "Automatic Dynamic Probe Setup" probe types.

| Pin Mapping                                                   |                                                                                             |                                                       | ×                                            |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------|

| Probes used to connect to<br>Reference Designator<br>J1<br>J2 | a your FPGA<br>Probe Type<br>Automatic Dynamic Probe Setup<br>Automatic Dynamic Probe Setup | Logic Analyzer Pod(s)<br>Slot D Pod 1<br>Slot D Pod 2 | Add Probe<br>View/Edit Probe<br>Delete Probe |

| <                                                             |                                                                                             | >                                                     |                                              |

|                                                               |                                                                                             | <u>O</u> K Cancel                                     | <u>H</u> elp                                 |

3 Select one of the automatically set up probes, and click Edit Probe....

| in Mapping |        |                |                |         |      | Đ              |

|------------|--------|----------------|----------------|---------|------|----------------|

| Core 0     | A      | utomatic Dyna  | mic Probe Set  | up      |      | Logic Analyzer |

|            |        | Reference Desi | ignator J1     |         |      |                |

|            |        |                | Ch 0 D0        |         | [    |                |

|            |        |                | Ch 1 D1        |         |      |                |

|            |        |                | Ch 2 D2        |         |      |                |

|            |        | ATD6           | Ch 3 D3        |         |      |                |

|            |        |                | Ch 4 D4        |         |      |                |

|            |        | ATD7           | Ch 5 D5        |         |      |                |

|            |        |                | Ch 6 D6        | Probe   |      |                |

|            | Drag _ | 1              | Ch 7 D7        |         |      |                |

|            |        | •              | Ch 8 D8        |         | Pod  | Slot D Pod 1   |

|            | Drop   | J              | Ch 9 D9        |         |      |                |

|            |        |                | Ch 10 D10      |         |      |                |

|            |        | ATD0           | Ch 11 D11      |         |      |                |

|            |        |                | Ch 12 D12      |         |      |                |

|            |        |                | Ch 13 D13      |         |      |                |

|            |        |                | Ch 14 D14      |         |      |                |

|            |        |                | Ch 15 D15      |         |      |                |

|            |        |                | Ch Clk         |         | l    |                |

|            |        | Show Logic     | Analyzer Chann | els     |      |                |

|            |        | <u>o</u> k     | Cancel         | ] Clear | Help |                |

|            |        |                | ,              |         |      |                |

4 Click **OK** to close the Pin Mapping dialogs.

To use graphical<br/>pin mapping1If you want to manually map pins using graphical pin mapping, click<br/>Pin Mapping... again.

| Choose Pin Mapping Method 🛛 🛛 🔀     |

|-------------------------------------|

| Automatic Pin Mapping (Recommended) |

| Graphical Pin Mapping               |

| Cancel                              |

- 2 In the Choose Pin Mapping Method dialog, click Graphical Pin Mapping....

- 3 In the Pin Mapping dialog, you can delete the automatically set up probes, and map pins as you would if the core was not plug-n-play (see To map pins for cores without auto pin-mapping (see page 34)).

- **Next** Measurement Step 4. Import signal names (see page 37)

### To map pins for cores without auto pin-mapping

1 In the Pin Mapping dialog (see page 66), click Add Probe....

| Probes used to connect to your FPGA |                      | Add Probe |

|-------------------------------------|----------------------|-----------|

| Reference Designator Probe Type     | Logic Analyzer Pod(s |           |

| <                                   |                      | >         |

2 In the "Select the type of probe to add" dialog, select the type of probe that is used to connect to your FPGA; then, click **OK**.

| Select the type of probe to add                                                                                                                                                                                                                                                                                                                                                                                                                      | × |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| E5404A 34-ch Pro Series soft touch connectorless single-ended probe<br>E5396A 17-ch Soft touch connectorless single-ended probe<br>E5396A 34-ch Soft touch connectorless single-ended probe<br>E5385A 34-ch Samtec single-ended probe<br>E5355I A 34-ch Mictor single-ended probe<br>E5336A 34-ch Mictor single-ended probe<br>E5339A 34-ch Mictor single-ended probe<br>E5339A 34-ch Mictor single-ended probe<br>E5338A Flying Leads (01650-61608) |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| OK Cance                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

If your probe doesn't appear in the list, you can "download the latest probe definitions from the web" (in the online help).

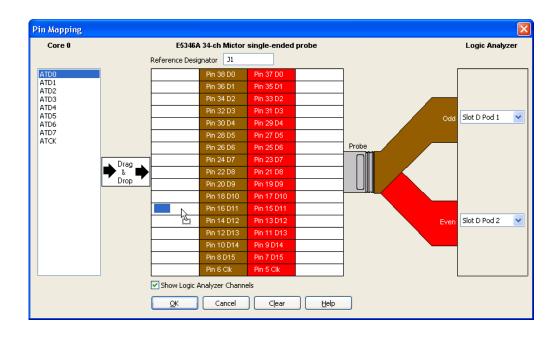

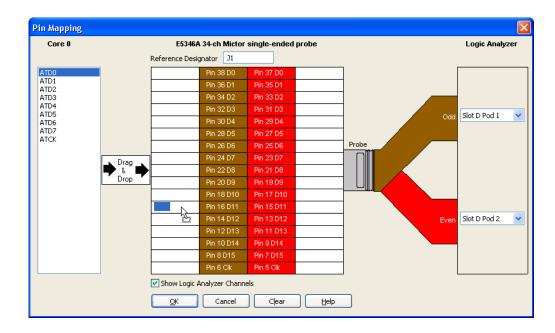

3 In the Pin Mapping Edit dialog (see page 67), select the FPGA pins (you can select multiple pins using Shift-click or Ctrl-click) and drag them on to the pin/pad map.

After you've mapped FPGA pins to the probe, you can hover the mouse pointer over a pin description field to view a tool tip describing the FPGA debug pin name, the pod connection, the channel number, and the signal type (single-ended or differential).

### 7 **Measurement Steps**

| E5346A<br>Reference Desig               | 34-ch Mictor<br>gnator J1 | single-ended | probe |

|-----------------------------------------|---------------------------|--------------|-------|

|                                         | Pin 38 D0                 | Pin 37 D0    |       |

|                                         | Pin 36 D1                 | Pin 35 D1    |       |

|                                         | Pin 34 D2                 | Pin 33 D2    |       |

| ATD6                                    | Pin 32 D3                 | Pin 31 D3    |       |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | Pin 30 D4                 | Pin 29 D4    |       |

| ATD7 Signal :                           | ATD6<br>od 1 Channel 3    | Pin 27 D5    |       |

|                                         | nded Signal               | Pin 25 D6    |       |

You can clear all FPGA pins that have been mapped to pins/pads by clicking **Clear**. You can clear individual pin mappings by dragging a pin from the pin/pad diagram back to the FPGA Pins list.

4 Select the logic analyzer pods that the probe is connected to.

When you wish to map multiple cores using different halves of the same probe, make sure you select **None** for the half that will be used by the other core.

For state (synchronous) cores, you need to make sure that the ATCK pin maps to one of the NOTE "Clk" pin/pad locations (which identify clock signal inputs) and that the associated logic analyzer pod is valid for clock inputs. (In the *General State Mode*, the clock lines on the first 4 pods of a logic analyzer can be used as clock inputs; in the Turbo State Mode, the clock line on the first pod can be used as a clock input.)

> 5 When you are done mapping FPGA pins, click **OK**. Note that your probe has been added to the list in the Pin Mapping dialog.

| obes used to connect t | o your FPGA                            |                           | Add Probe      |

|------------------------|----------------------------------------|---------------------------|----------------|

| Reference Designator   |                                        | Logic Analyzer Pod(s)     |                |

| ]]                     | E5346A 34-ch Mictor single-ended probe | Slot D Pod 1(Odd), Slot D | View/Edit Prob |

|                        |                                        |                           | Delete Prob    |

|                        |                                        |                           |                |

|                        |                                        |                           |                |

|                        |                                        |                           |                |

|                        |                                        |                           |                |

|                        |                                        |                           |                |

|                        |                                        |                           |                |

|                        |                                        |                           |                |

|                        |                                        |                           |                |

| <                      |                                        | >                         |                |

Click **OK** to close the Pin Mapping dialog.

Next Measurement Step 4. Import signal names (see page 37) ٠

## Measurement Step 4. Import signal names

The FPGA dynamic probe can automatically set up bus/signal names in the logic analyzer by reading a .cdc file produced by Xilinx Core Inserter.

To import bus/signal names:

1 In the FPGA Dynamic Probe Setup dialog (see page 64), select the device whose bus/signal names you want to import; then, click Import Bus/Signals....

| PGA I    | )ynamic I            | Probe Setup |                  |             |                                                      | Σ                         |

|----------|----------------------|-------------|------------------|-------------|------------------------------------------------------|---------------------------|

| On       | Device               | Core        | Imported Signals | Pin Mapping | Details                                              | Cable Connection          |

| <b>~</b> | Device 0<br>Device 1 | No Cores    |                  |             | XC18V00 - not configurable<br>XC2V250 - configurable | Device 1                  |

| <b>V</b> |                      | Core 0      | <none></none>    | J1, J2      | State, 64 banks, 9 pins                              | Configure Device          |

|          |                      |             |                  |             |                                                      | Import Bus/Signals        |

|          |                      |             |                  |             |                                                      | Core 0 Pin <u>Mapping</u> |

| <        |                      |             |                  |             | >                                                    | Properties                |

|          |                      |             |                  |             | <u> </u>                                             | ncel <u>H</u> elp         |

- 2 In the Select Signal Import File dialog (see page 69), select the signal import file; then, click **Open**.

- **3** In the Import Results dialog, view the bus/signal import information; then, click **OK**.

- 4 Click OK to close the FPGA Dynamic Probe Setup dialog.

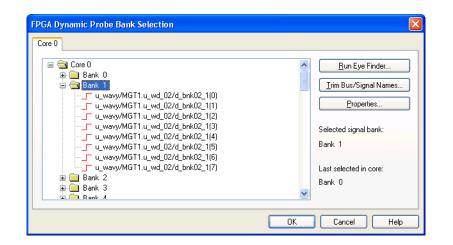

In the FPGA Dynamic Probe dialog, note that the imported bus/signal names appear.

| FPGA Dynamic Probe Bank Selection | ×                                                                                                                                                   |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Core 0                            | <u>R</u> un Eye Finder<br><u>Irim Bus/Signal Names</u><br><u>P</u> roperties<br>Selected signal bank:<br>Bank 0<br>Last selected in core:<br>Bank 0 |

| ОК                                | Cancel Help                                                                                                                                         |

Note also that you can triple-click signal names in this dialog to rename them (without having to do global trimming).

- See Also To trim imported bus/signal names (see page 38)

- To rename imported bus/signal names (see page 38)

- To define additional FPGA bus/signal names (see page 39)

- **Next** If you are using an MTC core or you have selected the state capture mode when inserting the ATC2 core (see page 21), see:

- Measurement Step 5. Adjust sampling positions for state (synchronous) cores (see page 41)

If you selected the timing capture mode when inserting the ATC2 core, see:

• Measurement Step 6. Make the measurement (see page 44)

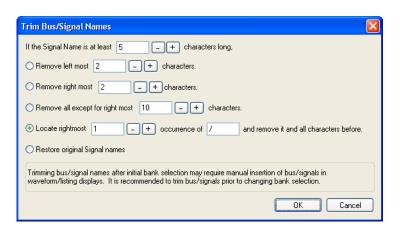

#### To trim imported bus/signal names

**NOTE** Trimming bus/signal names after initial bank selection may require manual insertion of bus/signals in Waveform and Listing display windows. We recommend that you trim bus/signal names before changing the bank selection.

**NOTE** Because the MicroBlaze inverse assembler relies on particular bus/signal names, do not trim bus/signal names from an MTC core.

- 1 In the FPGA Dynamic Probe Bank Selection dialog (see page 71), click **Trim Bus/Signal Names...**

- 2 In the Trim Bus/Signal Names dialog (see page 71), specify the bus/signal name characters to trim; then, click **OK**.

#### To rename imported bus/signal names

- 1 Open the Buses/Signals setup tab (see "Defining Buses and Signals" (in the online help)).

- 2 In the "FPGA Probe" bus/signal name folder, rename the bus/signal (see "To rename a bus or signal" (in the online help)).

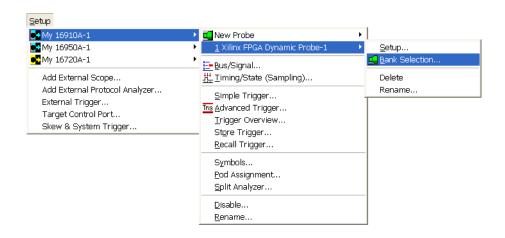

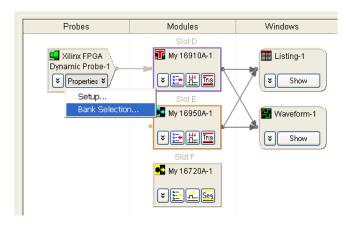

- 3 Reopen the FPGA Dynamic Probe dialog by choosing Setup>(Logic Analyzer Module)>(FPGA Dynamic Probe Name)>Bank Selection....

Or, in the Overview window, click the FGPA dynamic probe's **Properties** button; then, choose **Bank Selection...**.

#### To define additional FPGA bus/signal names

- 1 Open the Buses/Signals setup tab (see "Defining Buses and Signals" (in the online help)).

- 2 In the "FPGA Probe" bus/signal name folder, add a new bus/signal (see "To add a new bus or signal" (in the online help)).

- **3** Assign channels to the new bus/signal name (see "To assign channels in the default bit order" (in the online help) or "To assign channels, selecting the bit order" (in the online help)).

- 4 Reopen the FPGA Dynamic Probe dialog by choosing Setup>(Logic Analyzer Module)>(FPGA Dynamic Probe Name)>Bank Selection....

#### 7 Measurement Steps

Or, in the Overview window, click the FGPA dynamic probe's **Properties** button; then, choose **Bank Selection...**.

Whenever buses/signals are added to the "FPGA Probe" folder, they are associated with a specific bank. If you select another bank, the added buses/signals do not appear.

If you want to define buses/signals that apply to all banks, create them outside of the "FPGA Probe" folder. That way, the buses/signals are not associated with a bank.

## Measurement Step 5. Adjust sampling positions for state (synchronous) cores

When using MTC or ATC2 state (synchronous) cores, you can automatically adjust the logic analyzer's sampling positions to compensate for variances in signal paths. This results in extremely accurate measurements even on high-speed buses with narrow data valid windows. Agilent strongly recommends that you perform this step when using cores with 2X pin compression.

Agilent trace cores contain test generation circuitry to stimulate the signal banks and output pins. With this active data running, the logic analyzer invokes the *eye finder* feature to automatically adjust for variances in path delays through the core to the acquisition system on the logic analyzer.

To automatically adjust state mode sampling positions:

1 In the FPGA Dynamic Probe Bank Selection dialog (see page 71), select one of the banks probing internal FPGA signals.

| Core 0                                |                                                                                                                                 |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Core 0          Core 0         Sank 0 | <u>Bun Eye Finder</u> Im Bus/Signal Names <u>Properties</u> Selected signal bank:         Bank 0         Last selected in core: |

| Bank 2<br>Bank 2<br>Bank 3<br>Bank 4  | Last selected in core:<br>Bank 0                                                                                                |

- 2 Click Run Eye Finder....

- **3** In the "Thresholds and Sample Positions dialog" (in the online help), click **Run**.

| 🔆 Thresholds and Sample Positions 🛛 🛛 🔀             |                                                        |  |  |  |  |

|-----------------------------------------------------|--------------------------------------------------------|--|--|--|--|

| Legend<br>Current Sample Pos<br>Current Threshold ( |                                                        |  |  |  |  |

| Buses/Signals to Run                                | -5 -4 -3 -2 -1 0 1 2 3 4 5 ns Sample Position Messages |  |  |  |  |

|                                                     | tSample = -0.80 ns                                     |  |  |  |  |

| 🖃 🖓 Core 0 FPGA Pro                                 | tSample = -0.80 ns                                     |  |  |  |  |

| ⊡ u_wavy/u_                                         | tSample = -0.80 ns                                     |  |  |  |  |

| ₽ u_waw,                                            | tSample = -0.80 ns                                     |  |  |  |  |

|                                                     | tSample = -0.80 ns                                     |  |  |  |  |

| <b>⊻_</b> ⊏ u_wav,                                  | tSample = -0.80 ns                                     |  |  |  |  |

| <b>⊻_</b> _ u_wav,                                  | tSample = -0.80 ns                                     |  |  |  |  |

| ···· ✔ u_wav,                                       | tSample = -0.80 ns                                     |  |  |  |  |

| ⊻_⊏ u_wav,                                          | tSample = -0.80 ns                                     |  |  |  |  |

| ⊻_⊏ u_wav,                                          | tSample = -0.80 ns                                     |  |  |  |  |

|                                                     | tSample = -0.80 ns                                     |  |  |  |  |

| Run Auto Sample                                     | Position Setup 🔹 🛛 🔿 K Cancel Help 💡                   |  |  |  |  |

The Eye Finder dialog shows you the progress of the automatic sample positions adjustment.

| 🔆 Eye Finder [My 16910A-1] | X |

|----------------------------|---|

|                            |   |

| 50 %                       |   |

| Cancel                     |   |

When the automatic sample positions adjustment is complete, you can view the results in the Sample Positions dialog.

| K Thresholds and Sam                                | ple Positions     |                                                                      |                                 |                                            | X                       |

|-----------------------------------------------------|-------------------|----------------------------------------------------------------------|---------------------------------|--------------------------------------------|-------------------------|

| Legend<br>Current Sample Pos<br>Current Threshold ( |                   | <ul> <li>Suggested Sample Po</li> <li>Suggested Threshold</li> </ul> | sition 📄 Signal A<br>💻 Signal A | Activity Envelope Displa<br>Activity 14 Ch | annels Selected for Run |

| Buses/Signals to Run                                | -5 -4 -3<br>I I I |                                                                      | : 3 4 5m<br>I I I               | s Sample Position                          | Messages                |

| 🗄 🗹 🔀 My Bus 1                                      |                   |                                                                      |                                 | tSample = -0.90 ns avg                     | Expand bus to see r     |

| 🖃 🚔 Core 0 FPGA Pro                                 |                   |                                                                      | 1                               | tSample = -1.22 ns avg                     |                         |

| ⊡~ 🗹 📿 u_waw/u_ʻ                                    |                   |                                                                      |                                 | tSample = -1.22 ns avg                     |                         |

|                                                     |                   | ·                                                                    | · ·                             | tSample = -1.29 ns                         |                         |

|                                                     |                   | ·                                                                    | · ·                             | tSample = -1.29 ns                         |                         |

|                                                     |                   | ' <mark>   </mark> ' '                                               | 1                               | tSample = -0.92 ns                         |                         |

|                                                     |                   | ' <b>↓</b> ' <b> </b> ' ' '                                          | 1 1                             | tSample = -1.43 ns                         |                         |

|                                                     |                   | · <b>·</b> · · ·                                                     | 1                               | tSample = -1.14 ns                         |                         |

|                                                     |                   | ·                                                                    | 1 1                             | tSample = -1.29 ns                         |                         |

|                                                     |                   | · <b>I</b> · ·                                                       | 1                               | tSample = -1.14 ns                         |                         |

|                                                     |                   | •                                                                    |                                 | tSample = -1.29 ns                         |                         |

| Run Auto Sample                                     | e Position Setup  | ~                                                                    | •                               | OK Cance                                   | I Help                  |

**Test Bank** The Test Bank contains signals internally generated by the ATC2 core. This bank can be used as a first-pass method for adjusting state mode sampling positions, for example, when the internal FPGA signals do not generate a sufficient number of transitions or perhaps during early stages of debug if signals are not being generated properly.

| FPGA Dynamic Probe Bank Selection                                                                                                                                                                                                                                                         | ×                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core 0           Image: Bank 52           Image: Bank 53           Image: Bank 53           Image: Bank 54           Image: Bank 55           Image: Bank 56           Image: Bank 58           Image: Bank 59           Image: Bank 61           Image: Bank 63           Image: Bank 63 | <u>R</u> un Eye Finder <u>I</u> rim Bus/Signal Names <u>P</u> roperties         Selected signal bank:         Test Bank         Last selected in core:         Bank |

| ОК                                                                                                                                                                                                                                                                                        | Cancel Help                                                                                                                                                         |

**Next** • Measurement Step 6. Make the measurement (see page 44)

NOTE

## Measurement Step 6. Make the measurement

At this point, you are ready to use the logic analyzer (as you would normally) to capture activity on internal FPGA signals.

- Making Measurements with ATC2 Cores (see page 44)

- Making Measurements with MTC Cores (see page 46)

# **NOTE** Timing zoom is automatically disabled when using the FPGA dynamic probe. You can re-enable timing zoom; however, because of the ATC2 core, timing zoom does not provide an accurate representation of internal FPGA signals.

Captured data is invalidated whenever you:

- Select a different bank.

- Select a different core.

- Download configuration bits into an FPGA.

- Reopen a cable connection.

- Import signal names.

- Trim imported bus/signal names.

- Change the FPGA pin mapping.

#### **Making Measurements with ATC2 Cores**

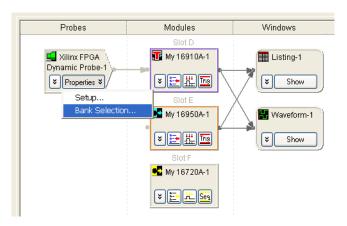

You can tell the ATC2 core to switch signal banks without affecting the timing of your design. When viewing the Probes toolbar (**View>Toolbars>Probes**), click <a>Imil to open the FPGA Dynamic Probe dialog. Then, select the signal bank to be routed to the logic analyzer and click **OK**. You can change signal banks as often as needed to make measurements throughout your FPGA.</a>

You can correlate internal FPGA activity with external measurements. With each new selection of a signal bank, the application updates new signal names from your design to the logic analyzer. View internal FPGA activity and time correlate internal FPGA measurements with external events in the surrounding system.

| Agilent Logic Analyzer - Unnamed Configuration - [Waveform-1]    |                |                      |                             |                                       |           |

|------------------------------------------------------------------|----------------|----------------------|-----------------------------|---------------------------------------|-----------|

| Eile Edit View Setup Tools Markers Run/Stop Waveform Window Help |                |                      |                             |                                       |           |

| ▋D ☞ 🖬 🖨 👬 🕷 🕨 T 💌   Q Q   🤫 📲 🖙 T 🗮 ▼ 🛅 ▼ 📗 💆 =   ⊠ 🔳 🕴         |                |                      |                             |                                       |           |

| M1 to M2 = 100 ns                                                |                |                      |                             |                                       |           |

| Scale 50 ns/div                                                  | tit tit Dela   | Os                   | I I                         | . 	.                                  |           |

| Bus/Signal                                                       | Simple Trigger | -100 ns              | -50 ns 0:<br>□   □ □ 1      | · · · · · · · · · · · · · · · · · · · | s 100 ns  |

| □ 🗍 u_wavy/MGT1.u_wd_0                                           | = * ×\$ •      | C6 X C8              | _XX                         | Св                                    | CC X CE 🔷 |

| -Du_wavy/MGT1.u_wd_                                              | X ×            | 0                    | 1                           |                                       | 0         |

| - 🖞 u_wavy/MGT1.u_wd_                                            | 1 ×            | 1                    | 0                           | 1                                     | 0 1       |

| - 🖞 u_wavy/MGT1.u_wd_                                            | 0 ¥            | 1                    | 0                           |                                       | 1         |

| - 🖞 u_wavy/MGT1.u_wd_                                            | 1 ×            | 0                    |                             | 1                                     |           |

| -∰u waw/MGT1.u wd                                                | X ×            | <                    | d                           |                                       | >         |

|                                                                  |                | H T - " My 169504-1" | ГТТ. ТТ <mark>Т-"Жү1</mark> | 9109-11                               |           |

| S Overview                                                       | Listing-1      | 🖁 Wavefor            | m-1                         |                                       |           |

| For Help, press F1                                               |                | Status               |                             |                                       |           |

#### **See Also** • "Capturing Data from the Device Under Test" (in the online help)

• "Analyzing the Captured Data" (in the online help)

#### **Making Measurements with MTC Cores**

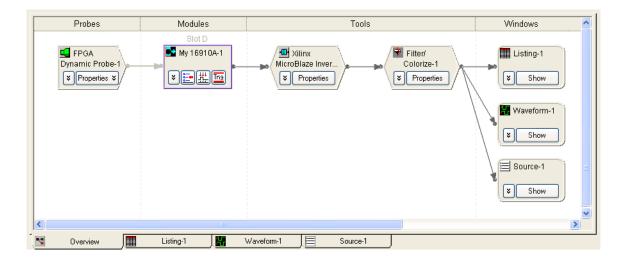

You can add the MicroBlaze inverse assembler tool to display captured data as assembly language mnemonics in the Listing window.

You can add a Filter/Colorize tool, for example, to hide wait states or add color for certain types of bus cycles.

You can add a Source window to display the high-level language code associated with the captured data.

For example, here is a Source window that shows captured MicroBlaze processor execution:

|                                                                                                                                                                                   |                                                                                                                                                                         | \mtx33.ala] - [Soi                                                                                                                    |                                                                                                                                                                                                                        |                 |                                                                                                                                                            |                                                                                                                                              |               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                                                                                                                                                                                   |                                                                                                                                                                         |                                                                                                                                       |                                                                                                                                                                                                                        |                 |                                                                                                                                                            |                                                                                                                                              |               |

| ) 🖻 🖬 🎒 🚧 '                                                                                                                                                                       | ัล 💰 💌 1                                                                                                                                                                | 「▶   Q, Q,   "                                                                                                                        | 5 🛛 🖬 🔁 📰                                                                                                                                                                                                              | i    🕨 🧔 🔳      | 🛛 🗶 🔳 📲 🦅 '                                                                                                                                                | シャッ;ャ/∥₽=₩                                                                                                                                   | Sea Mac 🐺 🥵 I |

| M1 to M2 = 640 ns                                                                                                                                                                 |                                                                                                                                                                         |                                                                                                                                       |                                                                                                                                                                                                                        |                 |                                                                                                                                                            |                                                                                                                                              |               |

| MI to MZ = 640 ns                                                                                                                                                                 |                                                                                                                                                                         |                                                                                                                                       |                                                                                                                                                                                                                        |                 |                                                                                                                                                            |                                                                                                                                              |               |

|                                                                                                                                                                                   |                                                                                                                                                                         |                                                                                                                                       |                                                                                                                                                                                                                        |                 |                                                                                                                                                            |                                                                                                                                              |               |

| Displayed File Z:\Do                                                                                                                                                              | cuments and Set                                                                                                                                                         | tings\\Core5\SPA\SI                                                                                                                   | PA.c                                                                                                                                                                                                                   | Browse          | ⇒{] <b>1</b> {                                                                                                                                             |                                                                                                                                              |               |

|                                                                                                                                                                                   |                                                                                                                                                                         |                                                                                                                                       |                                                                                                                                                                                                                        |                 |                                                                                                                                                            |                                                                                                                                              |               |

| 12 static int<br>13 OuterEntrv=                                                                                                                                                   |                                                                                                                                                                         |                                                                                                                                       |                                                                                                                                                                                                                        |                 |                                                                                                                                                            |                                                                                                                                              | ^             |